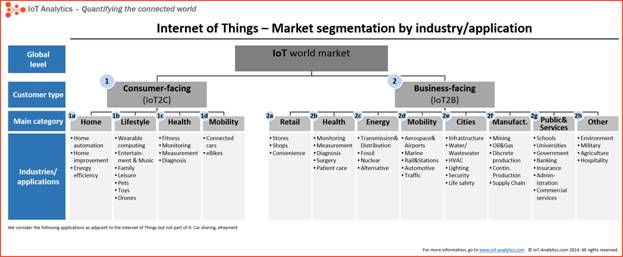

Fortune Business Insight predicts that the global Internet of Things (IoT) market will expand from $662.21 billion in 2023 to $3,352.97 billion by 2030, hence it is prevalent that the importance of IoT-enabled has a great future in the coming years.

Source: IoT market segments – Biggest opportunities in industrial manufacturing – IoT Analytics (iot-analytics.com)

Design-for-Test (DFT) is a crucial aspect of the semiconductor design process, ensuring that integrated circuits (ICs) can be thoroughly tested for functionality and reliability. In the context of Internet of Things (IoT) devices, where power efficiency, compact size, and connectivity are paramount, selecting the right DFT tools is essential. In this blog post, we will explore seven indispensable tools that should be considered in the DFT flow for IoT device design.

In the ever-evolving IoT device design, incorporating a robust DFT flow is indispensable. The selection of appropriate DFT tools plays a pivotal role in ensuring the reliability, efficiency, and longevity of these devices.

Major Complexities in IoT Design are:

- IoT Device Data volume checks at less interval of time: Each IoT device has its own hardware and may have different variants of software. It becomes difficult to test all the possible combinations of huge number of data volume under less test time at a low cost.

- IoT Device Faulty Behavior in deployment: In the IoT deployment, prevalent research analyzed that it is becoming complex in testing fault behavior in various elements including: i) Lower geometry nodes, ii) Sensor iii) Connectivity, and iv) Power consumption.

- Smart Memory chip design for IoT Device: It is one of the critical considerations in IoT applications. To meet the need of next-gen products, memory is moving up a level: traditional 8-bit flash memory to embedded flash memory to ultra-low-power memory. This growth came up with multiple issues like:

- Memory consumption needs to be tested thoroughly to know the response of the devices.

- IoT sensors run-out of memory when they are integrated with multiple signal requests into the device system.

- Leakage of memory if accurately not monitored during testing.

The below-mentioned sections dive deeper into testability tools to overcome the above-mentioned challenges in producing reliable IoT-enabled devices to achieve ~100% testability by ensuring proper functioning of the IoT design:

1. Scan Insertion:

- Tool Objective

- SCAN is a DFT design technique used in IC Design to increase the overall testability of a circuit. SCAN insertion architecture helps to test each of the logic elements in the IC irrespective of its position by inserting test vectors to device pins. It also helps to compress SCAN structure by inserting CODEC (Compressor De-Compressor) architecture, which will help to optimize the utilization of device pins for DFT purpose.

- Tool Description

- Synopsys – DFT Compiler is useful for implementing various DFT methodologies such as SCAN chain insertion, test point insertion, compression insertion, boundary scan insertion and core wrapping. It is useful for multi-level compressor-decompressor architecture implementation, which will be helpful in optimizing test data volume and test time reduction.

- Tessent – TestKompressis useful for SCAN insertion along with unique on-chip compression technique, which is helpful in optimizing test data volume and test time reduction.

DOWNLOAD CASE STUDY

Design for Testability for a High-speed Gigabit Ethernet Controller for Networking

DFT Solution and ASIC Design for a Gigabit Ethernet Controller | eInfochips

2. ATPG

- Tools Objective

- ATPG (Automatic Test Pattern Generation) is an automated algorithm programmed method to generate test patterns. The test patterns generated are used to test semiconductor devices in order to identify the cause of failure and segregate faulty devices and good devices based on its response.

- Tools Description

- Synopsys – TetraMAX ATPG is useful for various fault models and various formats of pattern generation having optimum runtime. It is useful to optimize pattern generation, coverage analysis, and debug.

- Tessent – FastScan is useful for optimized pattern generation of various fault models like stuck at, transition, multiple detect transitions, timing-aware, and critical path.

3. MBIST

- Tools Objective

- MBIST (Memory Built in Self-Test) is logically implemented within the chip to test memory. Because of the decreasing area and increasing complexity in memory, probability of the presence of manufacturing defect increases, testing memories in a chip is very critical.

- Tools Description

- Synopsys – SMS is a comprehensive, integrated test, repair and diagnostics solution that supports repairable or non-repairable embedded memories across foundries, process node and memory IP vendors. Its highly automated design implementation and diagnostic flow enables System-on-Chip (SoC) designers to achieve quick design closure and significantly improve time-to-market and time-to-yield in volume production. For More Information, Click Here

- Tessent – MBIST provides a complete solution for at-speed testing, diagnosis, and repair of embedded memory. The solution’s architecture is hierarchical, allowing BIST and self-repair capabilities to be added to individual cores as well as at the top level. It includes a unique comprehensive automation flow that provides design rule checking, test planning, integration, and verification all at the RTL or gate level. For More Information, Click Here

4. Boundary Scan and JTAG

- Tools Objective

- JTAG tools, which are based on the IEEE 1149.1 standard, provide a standardized interface for testing and debugging integrated circuits. In IoT device design, JTAG tools can be crucial for both manufacturing tests and in-field testing and diagnostics. There are multiple benefits of this IoT tool including efficient debugging, in-system programming, and support for in-field testing and updates.

- Tools Description

- Synopsys-Design Compiler (DFT Compiler) has boundary scan insertion feature.

5. Logical Equivalence

- Tools Objective

- Logical Equivalence check tools help to verify the design intended functionality remains the same before and after insertion of DFT architecture such as MBIST, SCAN and Boundary SCAN etc.

- Tools Description

- Synopsys Formality is useful for functional logical equivalence-checking (EC) for subsequent iteration of the design along with ECO cycle implementation.

- Cadence Conformal is useful for functional logical equivalence-checking (EC) for subsequent iteration of the design with minimal run time.

6. GLS

- Tools Objective

- GLS (Gate Level Simulation) is used to verify DFT architecture by performing simulation of ATPG patterns. It will help to identify if any discrepancy present in the MBIST, SCAN, and Boundary SCAN architectures.

- Tools Description

- Synopsys VCS is useful for test pattern simulation with optimum performance having minimal run time.

- Cadence Xcelium is useful for test pattern simulation with improved performance and having minimal run time with multi-core.

7. Visual Debug

- Tools Objective

- Visual Debug is the method widely used across the semiconductor industry to analyze the failures identified during GLS. It enhances the debugging capabilities of DFT engineer by visually analyzing signal values on failing logic elements/nodes.

- Tools Description

- Synopsys -Verdi is useful for design signal visual analysis by loading signal waveform dump and debugging the design signal connectivity in schematic by loading netlist for complex design.

- Cadence -SimVision is interactiveenvironment useful for design signal visual analysis and netlist schematic view analysis.

RELATED BLOG

When DFT engineers challenge the need for testability and its complexity in IoT device design, there are number of questions that need to be answered.

- Why do we need accuracy in next-gen product deployment?

- Why do we need testability in IoT functionalities?

- How to implement efficient lower geometry node design to achieve faster time to market?

For a better understanding and assistance on the above-mentioned questions and overall testability issues of the circuits that are likely to occur in your IoT Solution and Services’ chip’s DFT process, connect with the highly experienced eInfochips engineers. We work with various tier-1 product-based client organizations using the above-mentioned tools and have vast experience in it.

Would you like to learn more about how eInfochips help clients in DFT-DFM Architecture for IoT Devices? Get in touch with us.