All the portable devices ranging from smartphones, laptops, wearable technology, portable audios and even a car key require a longer battery life without the need to replace or recharge the batteries frequently. Device performance and battery life are critical factors in these systems. Historically, portable devices have low performance demands. However, this is no longer true. Modern AI/ML backed portable systems require high computational capability, and this performance must be achieved with extremely low power consumption to ensure acceptable battery life. Power management choices in these devices affect system reliability, operational cost, and efficiency.

With technology scaling, dynamic power is reduced because the operating voltage levels are also reduced. However, leakage power increased sharply. This happened due to the reduction in gate oxide thickness and stronger short-channel effects like Drain Induced Barrier Lowering (DIBL), which allow current to flow even when the transistor is in the OFF state. This off-state leakage continuously draws battery current even when the logic block is not switched on. The evolution of CMOS technology has influenced both power consumption and leakage in modern integrated circuits, making power management a critical design consideration. There is a direct relationship between supply voltage and dynamic power, as described by the power equation, where reducing voltage can significantly lower dynamic power consumption. In addition to dynamic and leakage power, short circuit power—arising during transistor switching—also contributes to overall power consumption.

Synthesis is a key stage in the ASIC design flow where the RTL is transformed into a gate-level netlist. This stage provides the earliest and most effective opportunity to apply power-reduction techniques and influence the overall power profile of the design. The implementation of power management techniques during synthesis is supported by advanced tools that enable low power synthesis. The capabilities of modern synthesis tools allow for the integration of various low power techniques, such as clock gating and multi-voltage design, to reduce power consumption. In integrated circuit and circuits design, dividing the design into different power domains is a common approach to optimize power efficiency. To implement various power reduction techniques, the design is divided into different power domains based on their architecture and functionality. These choices can have a significant impact on overall power efficiency and cost, especially in large-scale systems. These power domains are broadly classified into the categories below:

- Always-on domains

- Shut-off domains

- Retention domains

- DVFS domains (where lower performance blocks may operate at lower voltages as a trade-off)

Low Power Techniques

Designing for low power is a critical concern in modern ASIC and SoC development, especially as devices become more compact, portable, and performance-hungry. To achieve optimal energy efficiency and extend battery life, engineers employ a combination of low power techniques that target both dynamic and leakage power consumption throughout the design flow. Below are some of the most effective strategies used to reduce total power consumption while maintaining reliable performance.

Power Domains Explained

Let us take an example of a smartphone and a low-power micro-controller. These systems are broadly divided into below 4 domains:

- Always-on domains: These domains must remain powered-on all the time because they handle essential systems like the real-time clock (RTC), a power management unit (PMU), the boot ROM, and interrupt controllers. This domain can run at higher voltages for high-speed blocks and lower voltages for low-performance blocks. The PMU uses various controls to manage the sequencing and transitions between different power states of these domains.

- Shut-off domains: The blocks that consume significantly huge power but can be turned-off when not required. This includes GPUs, modems, SRAMs, camera ISP, and communication modules like Bluetooth and Wi-Fi. Shutdown procedures are managed by the PMU, which uses power switches to disconnect power from these domains and ensure proper isolation and retention during shutdown or sleep phases.

- Retention domains: These are registers and small memory banks that must save the state when rest of the block is powered off, for example a SRAM retention region.

- DVFS domains: Dynamic voltage frequency scaling enables voltage and clock period scaling to balance power and performance. This includes CPU cores, high performance processors, and ring oscillators to generate varied frequencies. Enable signals are used in clock gating logic to control which blocks are active, reducing switching activity and saving dynamic power.

The PMU decides the state of each block by controlling the transitions between different power states, such as active, sleep, and shutdown, using precise control signals and sequencing to optimize power consumption and maintain correct operation across voltage domains.

All the information that describes the power intent of a chip is coded in the Unified Power Format (UPF) or the Common Power format (CPF). UPF constructs such as create_power_switch are used to define power switches, which are implemented in the physical design to manage power domains and enable power gating for reducing leakage and dynamic power.

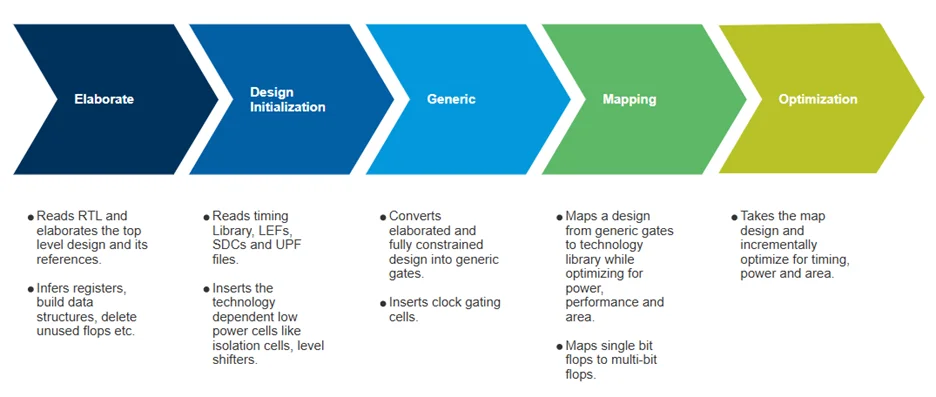

Low Power Synthesis: UPF-based low-power synthesis looks similar to normal single-domain synthesis, but the tool also checks the power intent and makes sure all optimizations follow the UPF and that they avoid any illegal domain crossings. Low power techniques like clock gating, power gating, and multi-voltage design are implemented in the design flow using UPF directives and specialized cells. The flowchart below shows the synthesis flow, and the table shows how different it is from regular synthesis:

| Aspects | Regular Synthesis | UPF-Aware Synthesis |

| Objective | Timing, area, and power optimization | Timing, area, power, and power intent correctness |

| Power domain awareness | Assumes single domain | Supports multiple power domains with UPF definitions |

| Low-power cells | Only clock-gating cells | Isolation cells, level shifters, retention cells, always-on buffers |

| Voltage Awareness | Single VDD | Multi-VDD awareness |

| Cross-domain handling | Not supported | Auto-inserts isolation and level shifter cells at illegal crossings |

| Retention logic | Not supported | Converts flops to retention flops as per UPF |

| Generated output | Gate-level netlist | Power-aware netlist containing all the power management logic |

| Post-synthesis Verification | Standard LEC | Power-aware LEC verification, conformal low power checks (VCLP) |

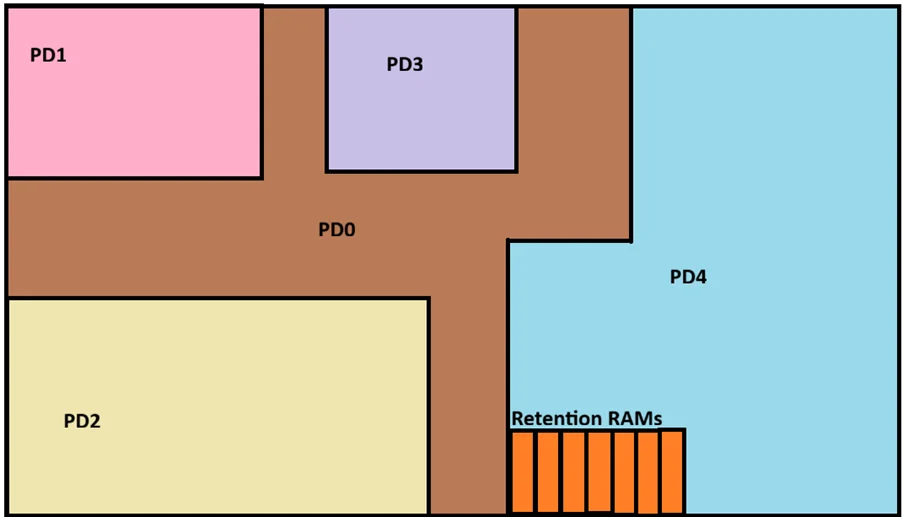

Illustrative example of low-power design:

This example shows how using multiple voltage domains and power-gating helps improve power efficiency. By dividing the design into separate power domains and turning off unused sections, we achieve a noticeable reduction in leakage and dynamic power without affecting performance.

Figure (i) Multi-voltage and Power Domains

| Power Domain | Attributes |

| PD0 |

|

| PD1 |

|

| PD2 |

|

| PD3 |

|

| PD4 |

|

As shown in the figure, we have multiple power domains with different attributes. The state in which a block/power domain would operate is decided by a power management unit (PMU) of the chip.

For the synthesis engine to understand the architecture described in figure(i), all this information must be coded in the UPF file. Few of the important UPF constructs are explained below:

- create_power domain: Creates all the 5-power domain based on their logical hierarchy.

- create_supply_set: Creates the power ground supply names in each power domain along with their voltage values.

- add_power_state: Describes the power state of the above created supply sets. These states describe which domains are ON, OFF, or retained.

- set_isolation: Describes isolation rules for the signals crossing the switchable domain to the always-ON domain. The synthesis tool adds the isolation cells based on the crossing defined in this rule.

- create_power_switch: Inserts power gates for the switchable power domain.

- set_level_shifter: Describes a level shifter rule for the signals crossing different voltage level domains.

Let us assume that the signals from all power domains communicate with each other. Based on the rules defined in UPF, the synthesis tool will add the low power cells below for the signal crossing from one power domain to another.

| PD0 | PD1 | PD2 | PD3 | PD4 | |

| PD0 | – | LS | None | LS | None |

| PD1 | LS+ISO | – | LS+ISO | LS+ISO | LS+ISO |

| PD2 | ISO | LS+ISO | – | LS+ISO | ISO |

| PD3 | LS | LS | LS | – | LS |

| PD4 | ISO | LS+ISO | ISO | LS+ISO | – |

Signals crossing from one switchable power domain to another switchable domain only requires isolation cells if the PMU is turning on and off the switchable domains at a different time. If they are switched on and off at the same time, no isolation cell is required.

The retention RAMs in PD4 operate normally when PD4 is ON. When PD4 is turned OFF, a small section of the RAM is still kept ON (at a lower voltage) to retain the required data. This data is restored and used again when PD4 is powered back ON.

Any failure to insert correct isolation and level shifter cells on the signal crossing from 1 domain to another would result in functional failure. Hence, the design needs to be thoroughly verified using LEC and CLP checks.

Conclusion

With technology scaling, leakage of power has become a dominant component of total power, making power-domain partitioning, UPF-driven synthesis, and techniques such as isolation, level shifting, and retention essential. Although these cells introduce some area, timing and power overhead, their overall benefits far outweigh these costs. Overall, a well-defined power intent combined with careful multi-domain design improves both silicon low-power SoC efficiency and design reliability, making these techniques critical for any low-power SoC today.

References

- Low Power Methodology Manual for System-on-Chip Design by Micheal Keating, Davind Flynn, Robert Aitken, Alan Gibbons, Kaijian Shi