In this blog, we will showcase how signal drive strength can be checked in SystemVerilog for best possible results, and the various rules which have to be observed in “documenting” signal strength.

According to basic principles of testing electronic systems, signal drive strength is considered one of the key metrics of signal integrity (SI). Whether you’re designing PCB, SoC, microcontroller, USB or any other electronic component, the ability to transmit the signal with high fidelity depends on signal drive strength. Drive strength can be used to resolve which value should appear on a net or gate output.

In a SystemVerilog test bench, it often happens that multiple drivers would try to drive a single net or output of gate. In this scenario, the output value is best determined based on the signal driving strength of each driver and its corresponding value.

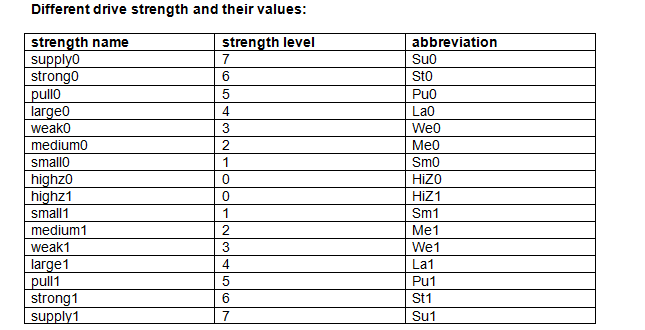

The following table has been derived from a SystemVerilog test bench spelling out different drive strength examples, their naming conventions, and abbreviation. Supply strength is strongest and high is the weakest.

Figure 1: Strength based on value

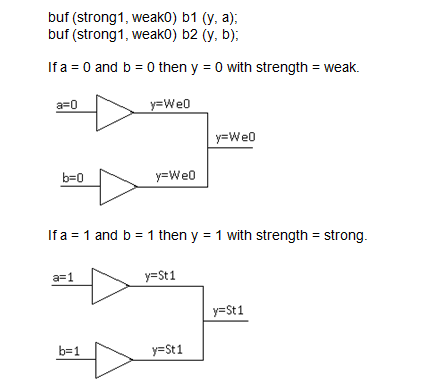

It is important to be able to check drive strength on a wire for a particular instance. Here’s an example that helps illustrate that.

Figure 2: Checking drive strength for a particular instance

[forminator_poll id=”8854″]

Any Gate (here we have taken example of buf) can be declared with drive strength as one of the following:

buf (strong1, weak0) #(10) b1 (out1, in1);

buf (weak0, strong1) #(10) b2 (out1, in1);

Or you can use assign statement as below:

assign (weak0, strong1) out1 = in1;

We can get the current value of drive strength using $sformatf and display it using %v

For example:

and (supply1, weak0) a1 (y,a,b);

str = $sformatf(“%v”, y);

$display(“Strength=%v Value=%b”, y, y);

Also, a few basic rules have to be kept in mind concerning signal drive strength.

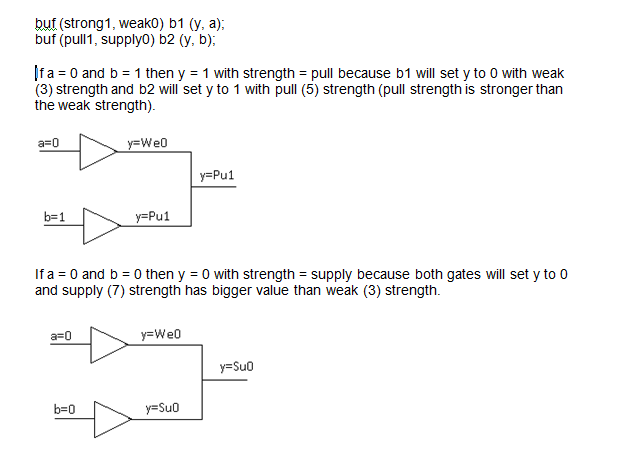

- If two drivers are driving a signal, then the signal with the strongest value will be considered

Figure 3: Signal with strongest value

- If two drivers are of the same strength and value, then the signal strength will remain same.

Figure 4: Signal of same value

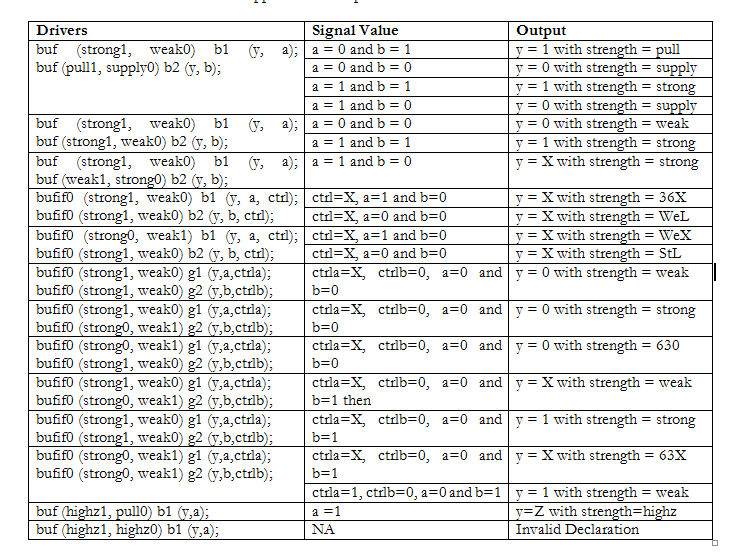

- When multiple drivers are present, the output signal’s value and strength depends on strength and values of all the drivers. See table below.

Table 1: Multiple Drivers scenario

As the evolution of SystemVerilog continues, it brings forth a host of noteworthy trends and advancements that hold the potential to shape the landscape of hardware description and verification languages. These developments carry significant implications for the ways in which engineers approach the design and verification of digital systems. Let’s explore some of the pivotal trends in the realm of SystemVerilog:

Emergence of RISC-V for Verification

Engineers are increasingly using RISC-V cores as part of their verification environments, helping to test and verify complex hardware systems more effectively.

Hardware Security Emphasis

With the growing concern over hardware security, SystemVerilog is witnessing an increased emphasis on security-related features. This includes constructs for modeling secure hardware components, implementing secure boot mechanisms, and verifying hardware against security threats.

The Rise of AI-Driven Verification

Artificial intelligence and machine learning are finding applications in hardware verification. AI-driven tools can automatically generate testbenches, analyze verification results, and even assist in debugging complex hardware designs.

Functional Safety Standards Integration

SystemVerilog is evolving to facilitate verification against these standards, with constructs for safety-critical hardware modeling and fault injection.

OpenLANE and Open Source ASIC Flow

The OpenLANE project and open-source ASIC flow are making ASIC design and verification more accessible. SystemVerilog is adapting to better integrate with open-source tools, enabling engineers to design and verify custom ASICs more efficiently.

Quantum Computing Verification

As quantum computing technology advances, SystemVerilog is facing the challenge of adapting to a fundamentally different computing paradigm. There is a growing need for verification methods to ensure the correctness of quantum hardware, and SystemVerilog might see developments in this area.

Enhanced Verification for Heterogeneous Computing

Heterogeneous computing systems, which combine CPUs, GPUs, and accelerators, are becoming more prevalent. SystemVerilog is evolving to provide better support for verifying the interactions between these diverse components and ensuring their seamless operation.

Mixed-Signal Verification Advancements

With the increasing complexity of mixed-signal systems, SystemVerilog is improving its support for mixed-signal verification. This includes more robust modeling of analog components and better integration with analog simulation tools.

Blockchain and Cryptocurrency Hardware Verification

Blockchain and cryptocurrency technologies require specialized hardware for mining and transaction processing. SystemVerilog is adapting to cater to the specific verification needs of these hardware components, including cryptographic modules and transaction processing units.

Real-time and Edge Computing Verification

SystemVerilog is evolving to address the unique challenges of real-time and edge computing applications. This includes verifying hardware components that must meet stringent timing requirements in low-latency environments.

Enhanced Visualization and Debugging Tools

Verification engineers are benefiting from improved visualization and debugging tools integrated with SystemVerilog environments. These tools enable better understanding and diagnosis of issues in complex hardware designs.

Quantum Dot Cellular Automata (QCA)

Quantum Dot Cellular Automata, an emerging nanotechnology, is gaining attention for its potential to revolutionize hardware design. SystemVerilog is expected to adapt to this technology, offering ways to model and verify QCA-based hardware. These trends reflect the evolving landscape of SystemVerilog and its crucial role in the design and verification of cutting-edge hardware systems. Staying informed about these trends is essential for engineers and designers to remain competitive in the ever-changing field of digital design.

YOU MAY LIKE THIS

To know more about signal driving strength, you can write to us at marketing@einfochips.com