Introduction

Analog-centric and digital-centric simulations are two different types of mixed-signal simulations. The real challenges appear when the simulation is analog-centric due to the large analog circuit. On the other hand, the digital-centric mixed-signal simulation is faster since the digital-centric mixed-signal simulation requires a digital kernel. Therefore, the mixed-signal simulation is categorized into two different ways based upon the types of the simulation engine. These are Co-simulation and Digital-centric simulation.

1. Mixed-Signal simulation (Co-simulation)

Any co-simulation is analog-centric. This means that there is a large analog circuit that has a small digital part inside it. The small digital part is controlled by the large analog circuit. The large analog circuit takes a long clock time to simulate the circuit. To reduce the simulation time, all the analog IPs must have simulation speed-up schematic views. These views are based upon the cells from the analogLib library only in the Virtuoso platform. The actual transistor-level design is made with standard schematic views. Therefore, there is no need to develop any model code using de facto standard model development languages such as Verilog AMS (electrical-based model) and System Verilog. There is no need for creating a Verilog AMS view of any analog design.

This methodology of developing simulation speed-up schematic instead of Verilog-AMS based model has certain advantages:

- The signal conversion models during mixed-signal co-simulation between the analog world and the digital world (or, in other words, the automatic insertion of connecting modules) are reduced, and as a result, the simulation speed improves.

- As the insertion of the connect module is removed on any particular net, the loading effect on that net is effectively modeled. Therefore, the signal continues from the source to the destination. This would not have been possible with the net and a connect module inserted on it, specifically, electrical to real or electrical to logic.

- A lot of time is invested in model development using languages such as Verilog AMS and System Verilog. Thus, we save on model development and model validation time as usually experts undertake model development using a language, and not the building analog blocks of the circuit design.

- The interaction among analog designers or the dependency on the analog designers is thus, reduced largely as there’s no need to develop any language-specific models for mixed-signal simulation.

Even though the said approach requires a little less than intermediate-level analog skills, the enormous advantages easily supersede the drawbacks.

2. Mixed-Signal simulation (Digital-Centric)

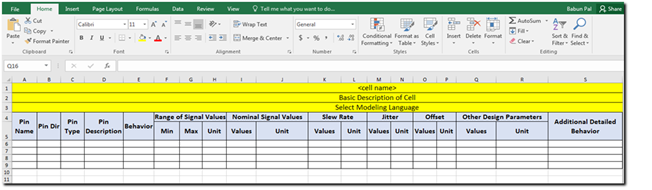

Nevertheless, for digital-centric simulation, Real Number Modeling (RNM) is the current trend for mixed-signal simulation. To leverage the advantages of digital UVM test bench setup, the model development flow is built-up with a standard model template that contains the columns of common features of any signal. This template must be filled-up by the analog designers.

Based upon the information provided by the analog designers, the model developer develops the model, validates them against the schematic, and then proceeds with the sign-off. It is to be noted here that the digital-centric simulation deals with the models that require digital solvers and no analog engine. Thus, digital-centric simulation doesn’t suffer from convergence issues. Hence, the simulation speeds up compared to the analog-centric approach.

Figure-1 shows a standard template. Analog designers fill up this model template. The model developers develop the model in the digital kernel. Therefore, analog designers’ input is very crucial in model development.

There are many advantages of using a template-based model development approach, such as:

- The analog design and model development can go in parallel.

- The model is verified only with the specifications based on the template. Once, the latest schematic is available, the model is validated against the schematic.

- The dependency on the designer is reduced.

- There is no need to read the schematic to develop the model.

- A specific model validation flow is set up based on the specifications provided with the template. Therefore, there is no need to use any EDA-specific tool for model verification against the specification and finally against the schematic.

Conclusion

Analog-centric mixed-signal simulation requires certain analog skills, whereas digital-centric mixed-signal simulation requires knowledge of data types. Thus, depending on the nature of the circuit (e.g. analog-centric circuit or digital-centric circuit), a specific verification methodology must be adopted. Consequently, for larger digital and small analog, circuitry requires a digital-centric mixed-signal verification methodology. Similarly, for large analog and small digital, circuitry requires a simulation speed-up model of analog IPs. Hence, the nature of the design (big A and small D or small A and big D) is key to opting for the verification methodology.

At eInfochips, we have verified sensor-based chips with Big A and Small D designs of the chips. We have also developed model and model validation of the DDR4 data buffer. We have expertise in both mixed-signal verification and model development and model validation. To know more please contact our experts today.