The most common elements of SoC architecture include one or more embedded processors (e.g. DSPs), functional units, interfaces of standard buses, timing sources e.g. oscillators, on-chip and off-chip memory and such. As the complexity of SoC increases and the size continues to decrease, accommodating the greater number of blocks/design units is a more complex procedure. This adds up in the overall elaboration time which also goes up, leading to lower yield and additional engineering costs in silicon design.

From the perspective of verification, one of the major challenges we face is reducing the rebuild time. Any minor change in the Verification environment requires re-elaboration of the complete environment, affecting productivity and efficiency of the engineers.

One of the approaches that helps us reduce the elaboration time at eInfochips is through the integration of MSIE ”Multi Snapshot Incremental Elaboration” flow.

Overview of MSIE

Verification engineers usually don’t make changes to the design under test (DUT) as they verify it using various test scenarios. They typically change only the verification environment (testbench or just the tests).

Using the same fundamentals, the Incisive Enterprise Simulator provides the ability to split the environment into parts that are elaborated separately and combined at the simulation step which is called MSIE ”Multi Snapshot Incremental Elaboration”. This capability enables faster elaboration of the design and verification environment in many common situations, including the following:

• Changes that are local to the testbench or the verification environment, but not in the design

• Linking different testbench hierarchies to a design that was already elaborated once

• Changes local to a design when the rest of the verification environment is unchanged (from a Designers perspective)

The last feature is most useful during the debugging phase as it enables very fast turnaround time after small modifications. It significantly boosts productivity and performance by separately elaborating the small changing portion from the once-elaborated or large fixed-portion of the design and verification environment. ASIC/SoC design project teams can deploy this technology to reduce the debug cycle time.

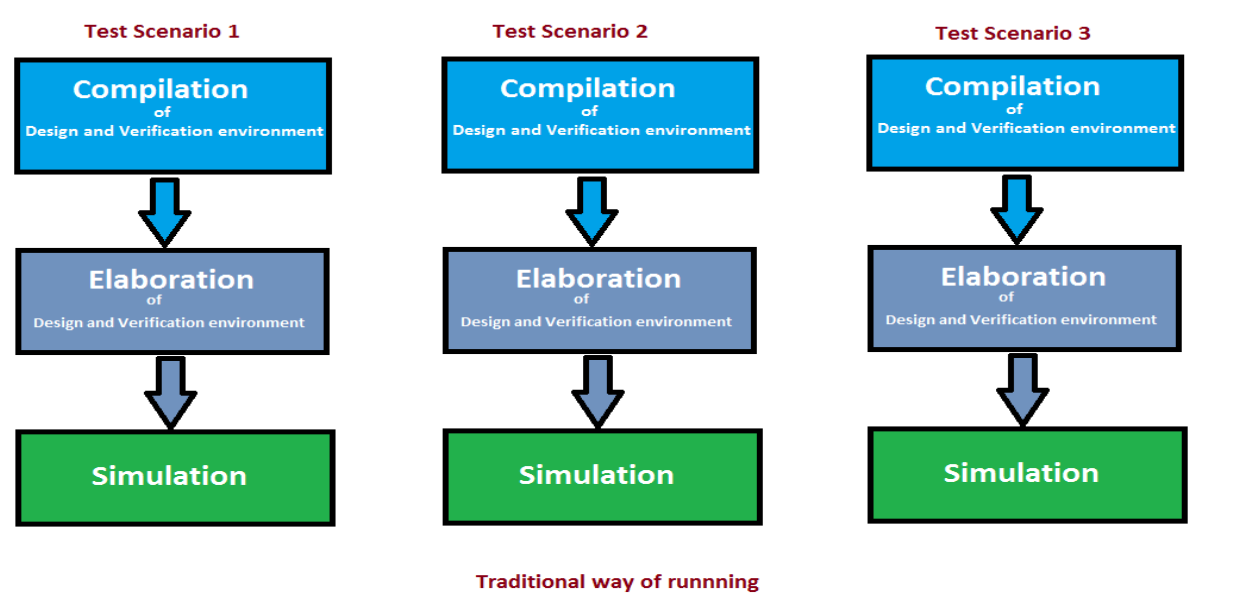

In the traditional way of running the simulation, entire DUT, verification environment and third party VIP, if any in the SoC should be compiled, elaborated and then simulated.

Figure 1: Traditional way of running simulation

Why MSIE

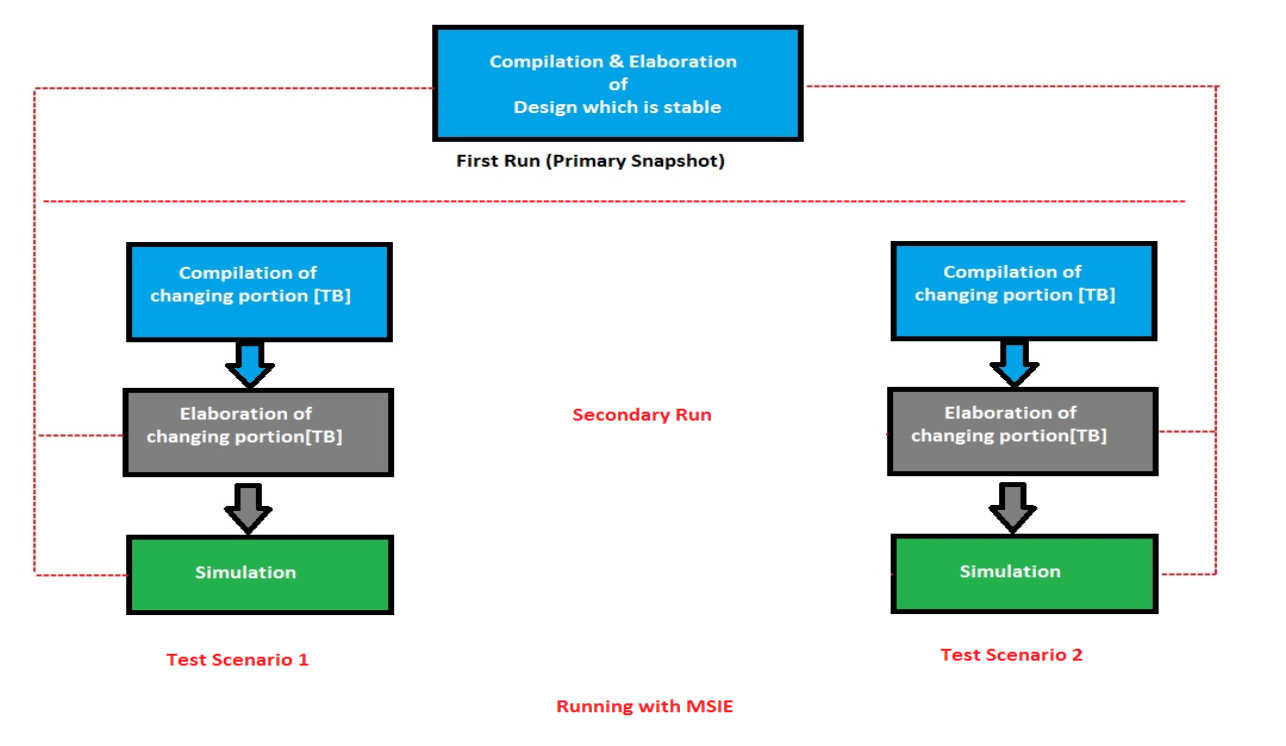

MSIE gives enterprises the flexibility to create pre-elaborated primary snapshots, which can be part of the designs, models and VIP packages that are stable and not expected to change very often. The smaller portion of complete environment that changes frequently, is elaborated as an Incremental snapshot. It is combined with the primary snapshot(s) for simulation.

Figure 2: Partitioning the DUT and verification environment

Primary snapshot of the DUT can be shared between multiple users in the SoC project. Rebuilds are extremely fast when change happens to incremental portion of the code. It leads to the significant time saving in the re-elaboration of the verification environment The following figure depicts the MSIE flow, the same primary snapshot is used for the multiple test scenarios which saves the compilation and elaboration of stable part.

Figure 3: MSIE flow of running

MSIE is also handful during Regression. For the larger SoC, huge number of test scenarios should be run the regression. This approach reduces the regression time as the complete compilation + elaboration + simualtion cycle time shortens due to saving in re-elaboration time

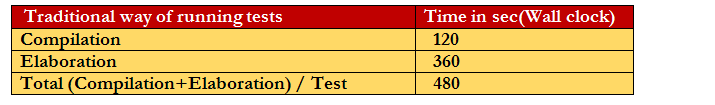

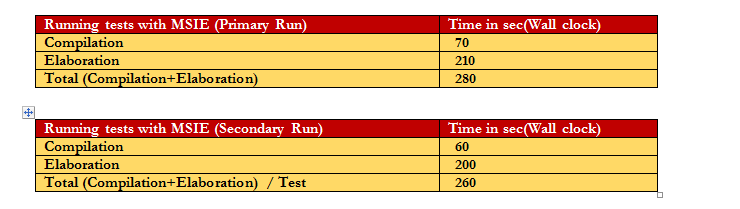

Statistics of Traditional simulation vs Simulation using MSIE:

– Total time taken to compile and elaborate ”n” tests in traditional way of running = (n x 480s)

– Total time taken to compile and elaborate ”n” tests using MSIE = (1 x 280s) + (n x 460s)

eInfochips has over two decades of experience in verification and validation among other services and has enabled multiple Fortune 500 companies to deliver high quality products on time.To know more about our services in verification, you can write to us at marketing@einfochips.com