According to Mordor Intelligence, the SoC is calculated at USD 159.85 billion in 2023, and it is anticipated to reach USD 234.98 billion by 2028, increasing at a CAGR of 8.01% during the forecast period (2023-2028).

System-on-a-chip (SOC) was only a catchphrase a few decades back. It is a necessary technology nowadays that keeps the electronics industry moving forward. Smaller, less expensive, quicker, and lower power-consuming computational devices are made possible by the growing trend of more integration and embedded computing, which is reflected in the rise in SoCs. Smartphones, tablets, routers, cameras, Internet of Things devices, and more all have SoCs.

System On Chip What is it?

SoC (System on Chip) are microchips that include all the required electronic circuits for a fully operating system on a Single Integrated Circuit (IC). Put otherwise, this means that the CPU, RAM, I/O ports, analog inputs and outputs, and extra circuit blocks are arranged in such a way that they can be integrated into a single chip. A distinct chip is utilized for the CPU, GPU, RAM, and other crucial functional components in conventional devices and PC designs. This is how SoCs vary from these systems.

SoCs are also produced according to target devices. Mobile network modems and Wi-Fi, for instance, may be integrated into SoCs used in smartphones and other Internet of Thing’s devices. In conventional methods, using shorter connections between circuit blocks, SoCs lower power consumption and boost efficiency.

Why SoC?

The fact that our major objectives going forward are to cut down on energy waste, save money on expenditures, and minimize the space taken up by massive systems is one of the driving forces behind the development of systems on a chip. By effectively condensing what are often multichip architectures onto a single processor that consumes far less power than before, a system-on-a-chip (SoC) accomplishes all of those objectives. Without ever having to sacrifice the gadgets’ usefulness or capabilities, these processors have allowed us to produce an abundance of portable electronics that we can easily take with us everywhere we go. As a result, embedded systems, IoT platforms, smartphones, and other gadgets frequently employ them.

System-on-a-chip has changed throughout the years, going from being only a word a few decades ago to becoming a crucial part of the electronics and technology sectors. In the real world, SoC applications are essentially infinite and invaluable. They are found in the majority of portable electronics, including tablets, smartphones, cameras, and other wireless devices. An excellent illustration of a system on a chip is your smartphone.

A lot more can be done on a phone than making and receiving phone calls, things such as browsing the internet, watching movies, listening to audio, taking pictures, playing games, and sending texts. But this is also true that several different parts, including a graphics card, wireless connections, internet connectivity, and GPS, play an important role, and without it would not work. All these parts can be included in a single chip using a system-on-a-chip (SoC), making it compact enough so that it can fit into the palm.

Advantages of System on Chip

There are several advantages to having several components integrated into one chip such as

- Space Maximization: Smaller device designs are made possible by SoCs since they occupy less space than several discrete components.

- Power Proficiency: SOCs replace massive components and circuits, resulting in a considerable decrease in power consumption and the achievement of the necessary PPA (power, performance, and area) criteria.

- Inexpensive: Compared to the collection of several independent chips that would otherwise be required, a single SoC chip is less expensive.

- Credibility: Compared to a multipart system connected via a substrate, a single SoC has fewer connections and is therefore far more dependable.

- Performance: An SoC can outperform a multipart solution in terms of speed and performance as the signals can remain on the chip.

SoC Development

Even while creating a SoC can have greater upfront expenses, many developers opt for this strategy to reduce power consumption and offer a great deal of differentiation. Traditionally, bus addresses and data cabling have used the great bulk of energy. Because SoCs have internal connections among their components, they require less cabling and use less power. Custom SoCs can also incorporate proprietary accelerators and intellectual property (IP) to improve performance and power economy.

Additional benefits of the SoC include enhanced performance and efficiency, simpler system designs, quicker time to market, increased security at the firmware and hardware levels, smaller, more compact chips, faster execution due to high-speed processors and memory, and simpler, more efficient system designs.

eInfochips is trusted by the semiconductor leaders and provides great key offerings and services in powering Next-Gen ASIC Design Services/FPGA-SoC Development and Verification.

In this section, we are going to discuss the SoC architecture and the development process steps.

SoC Architecture

A SoC architecture states a compounded joined circuit that involves all key components and circuits of a specific system. The part of SoCs comprises of CPU, GPU, Memory, I/O devices, etc. In this section, we are going to discuss about the SoC architecture-

Memory: In a system on a chip, memory is employed for storing. The memory might be volatile or non-volatile. RAM is a type of volatile memory. RAM has two different types: SRAM and DRAM. ROM is a part of the non-volatile memory.

Processor: It is the central component of a system on a chip (SoC), which normally has one or more coprocessors. It can be a DSP, microcontroller, or microprocessor. DSP is often employed as a processor in every system-on-a-chip.

DSP: Digital Signal Processor is what DSP stands for. It is a part of the SoC to handle signal processing tasks including gathering and analyzing data, among others. Additionally, it is employed to decode the photos.

Network Interface card: All of the constituent blocks in a SoC are connected via an internal interface, bus, or network. In essence, the network interface card connects the system to the network.

Encoder/Decoder: Information is interrupted and transformed into codes using this technique.

GPU: The Graphical Processing Unit, or GPU, is a part of the SoC that displays the user interface. GPU was created specifically to accelerate picture computing processes.

UART: The SoC comes with a Universal Asynchronous Receiver Transmitter that is utilized to send and receive serial data.

Peripheral devices: Peripheral devices are those with external connections, such as USB, HDMI, Wi-Fi, and Bluetooth interfaces. This device carries out several tasks in the SoC.

SoC Development Steps

The following figure shows the many steps that make up the SoC development process.

SoC Specification

The initial stage of any SoC development is defining requirements. Both the software and hardware components of the design need to adhere to the standards. Every interface that exists between the design and its surroundings must be fully described in the specifications.

SoC Architecture Design

The architectural design is produced after compiling all of the SoC specifications. The process of creating an architecture involves modeling the specifications both functionally and behaviorally. Data registers, buses, switches, on-chip and off-chip memory, combinational logic blocks, and finite state machines are all used to describe the design.

The design is divided at this point into the software and hardware components. In the latter phases of the design cycle, the software and hardware components are developed, tested, and improved simultaneously.

Software Development

We can no longer wait for hardware development to begin software development since new SoC designs are becoming more sophisticated. Thus, throughout the design phase, the SoC’s software and hardware are created and tested simultaneously. There are benefits to developing software early on such as it gives more time to market the product and establish the integration of hardware/software interfaces.

eInfochips has leveraged its expertise on Qualcomm SoCs and Android, and assisted in firmware development, merging, and testing across several variants for its client. To read more about the case study.

SoC Hardware development

Upon dividing the design into hardware and software components, the hardware components undergo several phases of development. We discuss more in detail about these development stages.

High-Level Modeling

Different hardware components are described abstractly algorithmically using high-level modeling. High-level languages like C, systemC, or others are typically used for this kind of modeling. As of right now, design restrictions are not a major source of worry.

RTL Design

Register Transfer Level is referred to as RTL. This degree of design abstraction is situated in between a structural and behavioral description of the intended circuit. A collection of registers and a set of transfer functions that define the data flow between the registers make up the circuit according to the RTL description. Verilog and VHDL are the languages most frequently used for RTL development.

eInfochips is the world leader in providing services in the semiconductor industry. One of the clients partnered with us by seeing eInfochips excellent track record for effortlessly managing complex RTL to GDSII implementation projects. To read more about the case studies.

Functional Simulation and Verification

Before proceeding to subsequent design stages, the functional accuracy of the produced RTL code must be confirmed. Every flaw discovered during the verification phase is reported, and the code is improved to address the problems. This stage ensures that the RTL code meets the design’s behavioral model and is logically valid.

Logic Synthesis

The process of converting RTL (Verilog or VHDL) code into a gate-level netlist that represents the hardware—logic gates and wire connectivity—is known as logic synthesis. The three phases of the synthesis process are mapping, translation, and optimization. These three processes are used to translate RTL code into a gate-level netlist.

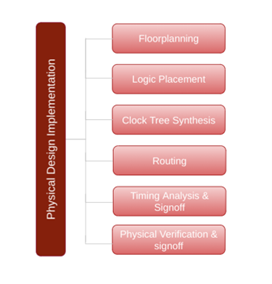

Physical Design Implementation

The process of converting the gate-level netlist into a physical layout is called physical design. This physical configuration is made up of different metal sizes and shapes that can be fabricated on silicon wafers and drawn onto masks.

The physical design implementation is categorized into several stages as shown in the diagram below-

Floor planning

The initial stage of physical design is floor planning. By the system architecture and design specifications, the design is first divided into several smaller subsystems. The layout’s size and aspect ratio are determined by floor planning.

Logic Placement

At this point, every standard cell in the design has been positioned and given a valid placement. EDA tools carry out several improvements to enhance placement and congestion after placement. Inadequate positioning might result in increased space usage and scheduling problems.

Clock Tree Synthesis

In the stage of floor planning and placement, the clock is seen as the perfect network. The placement stage optimizations are carried out under the presumption that an optimal clock reaches every flop simultaneously. To spread the clock throughout all of the flops in CTS, a clock network is built.

Routing

All of the linking data nets must be arranged on the metal layers once the clock network has been synthesized and all of the standard cells have been positioned properly. During the routing phase, this is completed.

Timing Analysis & Signoff

Static time analysis is done on the design following routing. This stage is essential for evaluating the design’s performance. We divide the design into time-based pathways during STA and figure out the signal propagation delay along each path. Next, if there are any time-based constraint violations, each path is examined. If there are any path infractions, they must be fixed before the design is approved.

The timing signoff guarantees that the design is operating at the desired frequency and that all design parts adhere to the timing specifications.

Physical Verification & Signoff

To guarantee that the layout has the proper electrical and logical functioning, it must be thoroughly tested when routing is finished. The physical verification signoff guarantees that the design is easily fabricated and complies with all fabrication specifications. At this point, many inspections are carried out, including:

DRC (Design Rule Check)

LVS (Layout Vs Schematic)

ERC (Electrical Rule Check)

Antenna check

EM (Electromigration Analysis)

Conclusion

The need for SoC innovation will persist because of the growing need for faster and smarter electronics in more demanding environments. In general, engineers aim to progressively miniaturize equipment, save money, and minimize energy waste. This is made feasible by system-on-chip technology’s sophisticated integration techniques on a single IC.

The development of smartphones has been fueled by these tiny, multipurpose processors, which offer amazing capability in a little package. Similarly, manufacturers are incorporating SoCs into new embedded systems, IoT devices, and even cars because of their compact size and power efficiency. For more information, you can refer to this tweaker in VLSI.