Introduction:

In different SOCs, memory is mostly treated as a peripheral component to be shared with other interconnected components. To prevent the problem of memory overwrite, ARM’s Advanced Microcontroller Bus Architecture (AMBA AXI), universally known for its use in portable smartphone-like devices, is a surefire way to provide exclusive access. This may look simple at first glance, but there are so many different flavors of exclusive access that the entire topic deserves proper detailing. Accordingly, this blog focuses on exclusive access in AMBA AXI3, its concept, and various flavors.

Exclusive Access – The Concept

Simple exclusive accesses happen to be a sequence of read transactions followed by write transactions in a same address range. Successful exclusive access receives an EXOKAY response. All other accesses, including failed exclusive accesses, receive an OKAY response.

The exclusive access mechanism enables the bus in such a way that it will not remain locked to a particular master for the duration of an operation. The exclusive access is used to achieve the maximum possible bandwidth which is similar to a semaphore-type operation.

Fact remains that the delays between exclusive read-and-write transactions and an exclusive sequence is undefined in the beginning. However, exclusive sequences start with an exclusive read operation and then, assuming the slave returns a successful EXOKAY response for the same read operation, the master can complete an exclusive sequence with exclusive write.

The exclusive write of a master is signaled as “successful” if no other master has written to that location between the read and write transactions. It is signaled as “failure” if another master has written to that location between the read and write transactions. In this case, the address location is not updated.

System Level Perspective

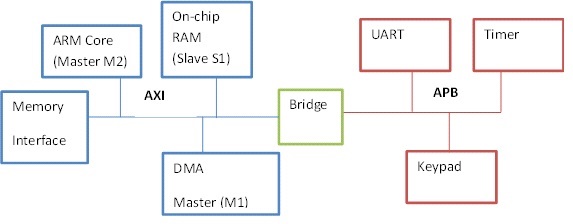

The exclusive access plays a critical role where more than a single master is trying to access the same slave (a memory) in a system. In technical terms, such types of slave memory is called a shared memory. A designer will always try to ensure that at a given point of time, one master does not corrupt the memory written by another.

Assume there are 2 AXI masters in a system sharing the same memory (slave S1) which supports exclusive access. Master 1 (M1) initiates exclusive read transaction for address location 16?h0000 to 16?h000F. The slave will start monitoring these addresses for ARID given by M1 until either a write occurs to the same location, or another exclusive read with the same ARID value resets the monitor to a different address.

If master M2 writes to the same address location of S1 before M1 could complete its exclusive write, the slave will give indication of exclusive access operation failure during the exclusive write transaction by M1 and does not allow M1 to update the slave memory location.

In the above system level scenario, the slave monitors (reserves) some memory locations for M1 as indicated by the exclusive read request from M1. When M1 attempts a write to this memory location, the slave will allow writing to that memory location only if another master device is not using that memory location, otherwise data is not written to the memory location. This way we can prevent memory overwrite/corruption problem for shared memory using exclusive access of AXI.

What are the different flavors of Exclusive Access?

There can be different scenarios of exclusive access operation. Some of these tricky flavors are highlighted below:

- An exclusive read can be followed by normal read or write.

- A master might not start the write portion of an exclusive operation.

- An exclusive read can follow another exclusive read with the same ARID value as previous exclusive read, and reset the slave monitor to a different address location of slave memory.

- There can be two exclusive read operations monitoring the same address region.

- An exclusive read/write to a slave memory does not support exclusive access.

Summary

Using the methodology described in the given text, the problem of memory overwriting can be avoided where multiple masters and multiple slaves can safely interact through AMBA AXI bus.

eInfochips is part of the ARM Approved Partner Program which helps companies deliver success in SOC design services based around ARM cores. eInfochips has a strong track record in delivering successful design projects around ARM cortex-M0 IP. eInfochips has developed its own libraries of IP which help in achieving faster time-to-market for end customers.

To know more about eInfochips breadth of offerings in ASIC/SOC design.