Due to immense complexities in Analog Mixed Signal SoC’s/chips, there is an intrinsic need for automation in the methodology or flow to provide confidence on Command Line based Mixed Signal Verification as shown in Figure 1. The UVM-MS methodology is a command line based (or file based) approach and in that methodology, the AMS test bench set up files (e.g. amscf.scs, amsbind.scs etc.) can be auto generated with the help of config view (a configuration view which is created using Hierarchy editor in GUI mode) using runams script that these files could readily be used while running simulation with irun.

This article describes how AMS test bench setup files can be auto-generated using runams script and be used in the command line based AMS verification.

This blog covers challenges faced in mixed signal verification and debugging in a AMS verification cycle #MixedSignal #Semiconductor #AMSVerification via @einfochipsltd

Mixed signal verification challenges

The analog verification methodology is traditionally ad-hoc by nature, lacking the formalized methodology that is available on the digital side. Digital verification team now have access to the verification plans, constrained-random stimulus generation, test bench automation, assertions, and coverage metrics. In digital design, the metric-driven verification approach, standardized for reusability as Universal Verification Methodology (UVM) helps engineers build confidence in the verification by increasing coverage to the desired level. On the analog side, verification is driven by directed tests run over sweeps, corners, and Monte Carlo analysis. Several analog solvers today provide low-level device checks, but there is little or no support for verification planning or coverage metrics.

RELATED CONTENT

Debugging of Mixed Signal SoC in an effective and efficient way to save multi-billion $ loss

To overcome the above mentioned challenges, command line based UVM methodology must be adopted in verilog AMS verification as explained below.

Advantages of this methodology

There is minimal human intervention required to setup command line based AMS verification flow.

- The files will be auto generated by the script and hence lesser human errors.

- Config view of analog designer can be readily used in this flow.

- Faster time to setup AMS test bench in UVM based AMS verification.

What is command line based AMS verification?

In command line based verification, we generally deal with many files which have co-relation with each other.

With command line based verification, we run “irun” script with some of its options e.g.

irun –clean –f file_list.fl –timescale 1ns/1ps

The file_list.fl file contains the following list of files:

- cds_globals.vams

- userDisciplines.vams

- amscf.scs

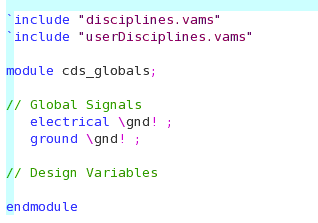

cds_globals.vams file will look like this:

userDisciplines.vams file will look like this:

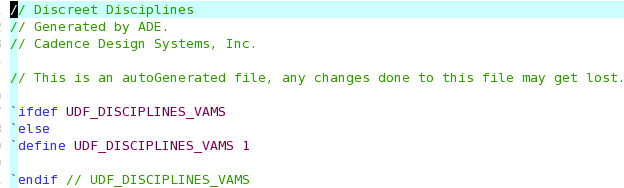

amscf.scs is the ams configuration file which looks like this:

Now, the next question could be “How can we convert GUI mode based method into command line based method”?

Below is the flow chart of steps to be executed in order to convert a GUI mode based flow into a command line based methodology.

When we run the “runams” script, we get the following files generated that these files will be used in the command line based AMS verification. E.g.

runams –lib ADC –cell flash_adc –view config –netlist –rundir top_run1

- .amsbind.scs

- spiceModels.scs

- amsControlSpectre.scs

The .amsbind.scs file binds the amsd control block for config view. An amsbind.scs file which is auto-generated looks like below:

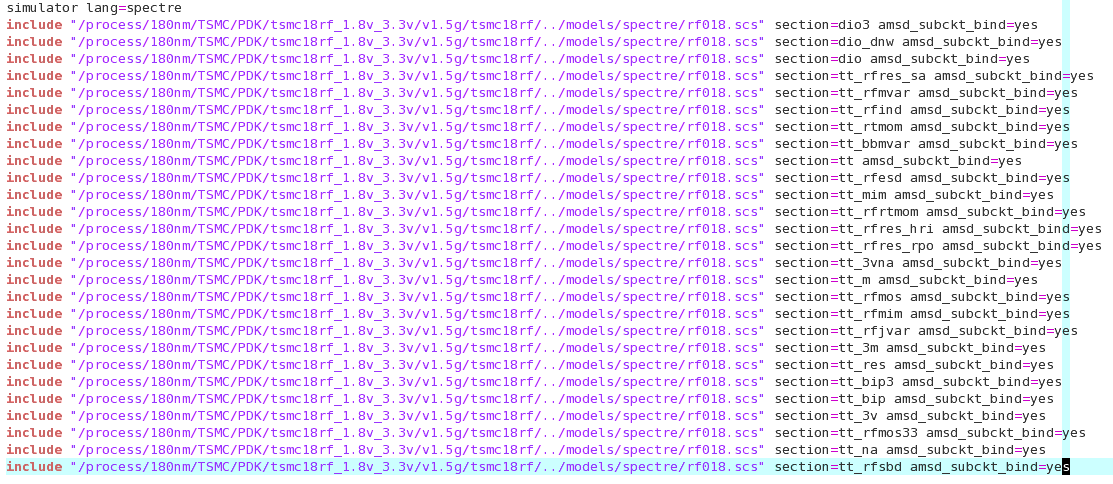

A typical spiceModels.scs file which is auto-generated looks like below:

A typical amsControlSpectre.scs file which is auto-generated looks like below:

Why should we consider this flow?

The approach to verify a Mixed-signal SoC is time consuming and also very complex. Because, it requires to generate spectre netlist of the Schematic view and manual configuration using portmap. Hence, majority of time in verification is spent on AMS setup/bring up. There is a demand to save the time and for that certain steps have to be automated.

This flow is simple and easily automated to setup the AMS engineering flow in UVM based (command line based) AMS verification and if the design is complex then it saves a lot of time in AMS semiconductor environment bring up.

Know more about Analog Mixed Signal Verification Methodology

Accelerate your product quality with AMS verification setup in Analog Mixed Signal SoC’s/chips