Modern System-on-Chips (SoC) are a complex island of logic, surrounded by a sea of memory. Embedded memories make up more than 70% of the consumer electronics design. Memory models are special kinds of verification IPs with a layer that has information specific to supported memory types. It enables designers to quickly and efficiently verify the standard part of the design and takes the load of gaining expertise on memory protocols off the verification engineer’s to-do list. Integrating and maintaining multiple memory models and re-creating the verification environment demands a lot of effort.

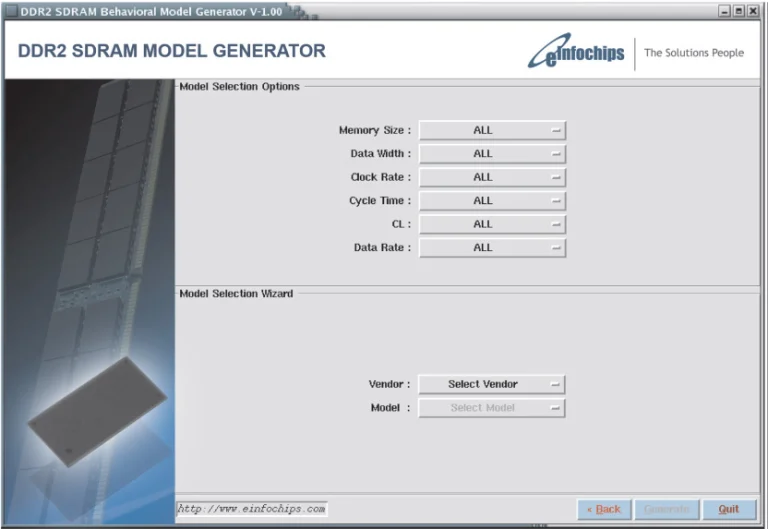

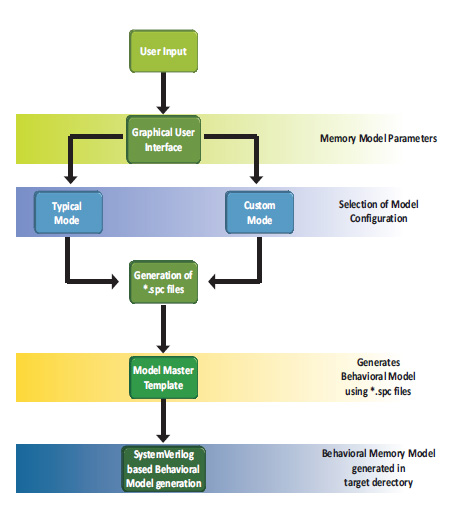

The eInfochips Memory DIY Framework is a GUI (Graphical User Interface) based memory model generation tool that supports the latest memory types including LPDDR and DDR and their configurations. It generates a SystemVerilog based behavioural model that can be integrated in the verification infrastructure and supports multiple vendors in a single package that needs to be integrated only once. The tool also comes with a pre-verified regression package that can run for multiple vendors in a single execution. The tool can further support the constrained-random, coverage-driven methodology for verifying memory interfaces & system correctness.

INTERLAKEN VIP comprises of following major elements:

- DDR Behavioral Model

- Generator

- Driver

- Collector

- Scoreboard

- Coverage

- Pre-integrated testcases

Features

- Allows the user to generate customized memory models

- Reduces verification efforts and enhances verification coverage

- Low-cost HVL based solution with ease of use and ease of integration

- TCL/TK based GUI, no special system specifications required

- Fully compliant to JEDEC standard