Les systèmes sur puce modernes sont des îlots logiques complexes entourés d'une mer de mémoires. Les mémoires intégrées représentent plus de 70 % de la conception des produits électroniques grand public. Les modèles de mémoire sont des types spéciaux d'IP de vérification avec une couche qui contient des informations spécifiques aux types de mémoire pris en charge. Ils permettent aux concepteurs de vérifier rapidement et efficacement la partie standard de la conception et enlèvent à l'ingénieur de vérification la charge d'acquérir une expertise sur les protocoles de mémoire. L'intégration et la maintenance de plusieurs modèles de mémoire et la recréation de l'environnement de vérification demandent beaucoup d'efforts.

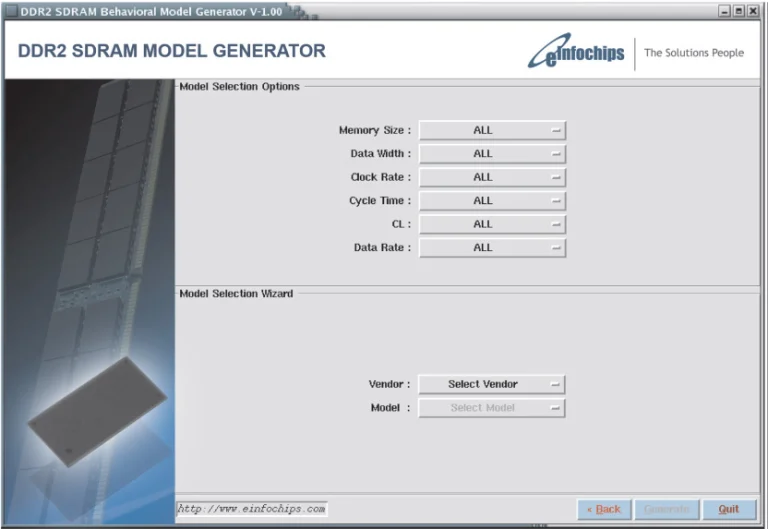

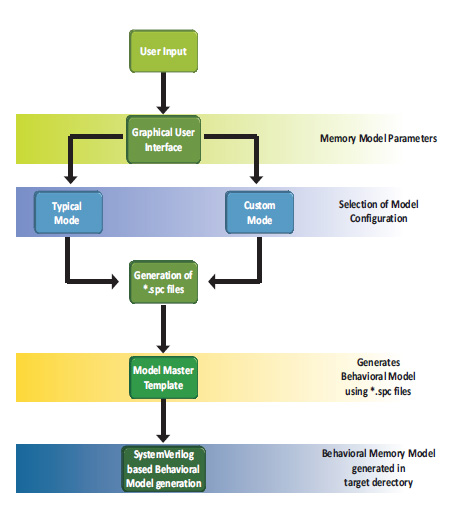

Le cadre eInfochips Memory DIY est un outil de génération de modèles de mémoire basé sur une interface utilisateur graphique (GUI) qui prend en charge les derniers types de mémoire, y compris LPDDR et DDR, ainsi que leurs configurations. Il génère un modèle comportemental basé sur SystemVerilog qui peut être intégré dans l'infrastructure de vérification et supporte plusieurs fournisseurs dans un seul package qui ne doit être intégré qu'une seule fois. L'outil est également fourni avec un ensemble de régression pré-vérifié qui peut être exécuté pour plusieurs fournisseurs en une seule fois. L'outil peut également prendre en charge la méthodologie aléatoire contrainte, axée sur la couverture, pour la vérification des interfaces de mémoire et de l'exactitude du système.

INTERLAKEN VIP comprend les principaux éléments suivants :

Caractéristiques

Prenez rendez-vous pour une consultation de 30 minutes avec nos experts en solutions automobiles

Prenez rendez-vous pour une consultation de 30 minutes avec notre expert en solutions de gestion de batteries

Prenez rendez-vous pour une consultation de 30 minutes avec nos expertsen solutions industrielles et énergétiques

Prenez rendez-vous pour une consultation de 30 minutes avec nos experts