Moderne System-on-Chips (SoC) sind komplexe Logikinseln, die von einem Meer aus Speicher umgeben sind. Eingebettete Speicher machen mehr als 70 % des Designs in der Unterhaltungselektronik aus. Speichermodelle sind spezielle Arten von Verifikations-IPs mit einer Ebene, die spezifische Informationen zu den unterstützten Speichertypen enthält. Sie ermöglichen es Designern, den Standardteil des Designs schnell und effizient zu verifizieren, und entlasten den Verifikationsingenieur von der Aufgabe, sich Fachwissen über Speicherprotokolle anzueignen. Die Integration und Pflege mehrerer Speichermodelle sowie die Neugestaltung der Verifikationsumgebung erfordern einen hohen Aufwand.

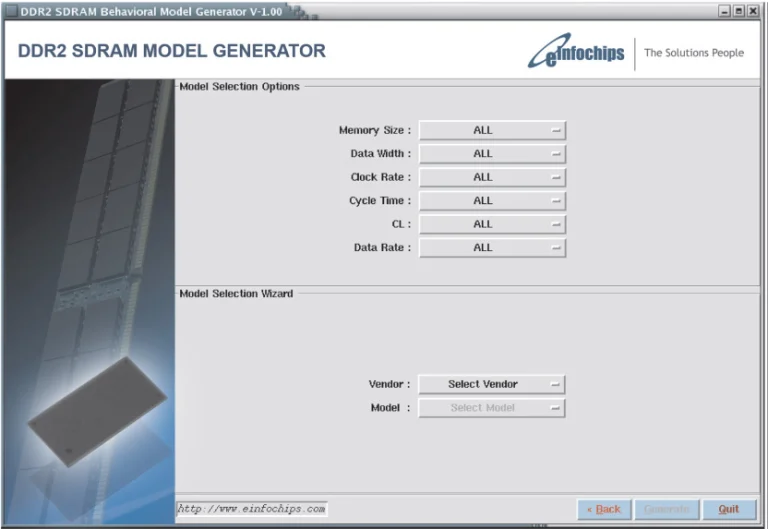

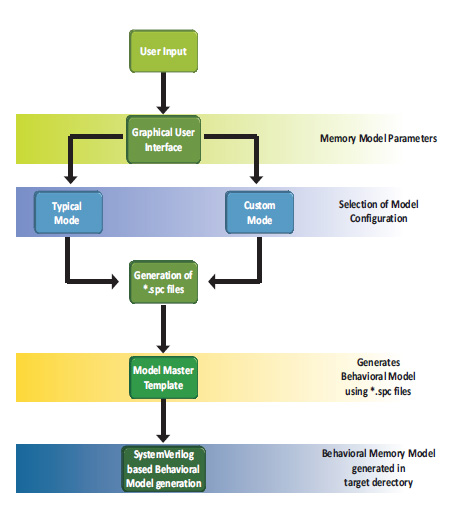

Das eInfochips Memory DIY Framework ist ein auf einer grafischen Benutzeroberfläche (GUI) basierendes Tool zur Generierung von Speichermodellen, das die neuesten Speichertypen wie LPDDR und DDR sowie deren Konfigurationen unterstützt. Es generiert ein auf SystemVerilog basierendes Verhaltensmodell, das in die Verifikationsinfrastruktur integriert werden kann, und unterstützt mehrere Anbieter in einem einzigen Paket, das nur einmal integriert werden muss. Das Tool enthält außerdem ein vorverifiziertes Regressionspaket, das für mehrere Anbieter in einer einzigen Ausführung laufen kann. Das Tool unterstützt darüber hinaus die Constrained-Random-Methode zur Verifikation von Speicherschnittstellen und der Systemkorrektheit.

INTERLAKEN VIP umfasst folgende Hauptkomponenten:

Funktionen

Vereinbaren Sie ein 30-minütiges Beratungsgespräch mit unseren Experten für Automobil-Lösungen

Vereinbaren Sie ein 30-minütiges Beratungsgespräch mit unserem Experten für Batteriemanagementlösungen

Vereinbaren Sie ein 30-minütiges Beratungsgespräch mit unseren Expertenfür Industrie- und Energielösungen

Vereinbaren Sie ein 30-minütiges Beratungsgespräch mit unseren Experten