Weltweit arbeiten Ingenieurteams gemeinsam daran, zukunftsweisende Technologien in winzigen ASICs (Application Specific Integrated Circuit) zu entwickeln. In diesem spannenden Wettlauf geht es darum, kompakte, schnellere und effizientere Designs für integrierte Schaltungen (IC) zu finden, um Zukunftstechnologien zu entwickeln. In einem von Grand View Research veröffentlichten Bericht wird die Größe des weltweiten Marktes für anwendungsspezifische integrierte Schaltungen (ASIC) im Jahr 2022 auf 15,99 Mrd. USD geschätzt, und von 2023 bis 2030 wird ein Wachstum mit einer CAGR von 5,9 % erwartet.

Anwendungsspezifische integrierte Schaltungen (ASIC): Was sind sie?

ASIC-Design ist ein Prozess zur Verringerung der Größe und der Kosten einer elektronischen Schaltung, eines Produkts oder eines Systems. Dies geschieht durch die Reduzierung und Integration einer einzelnen Komponente und ihrer Leistung in ein einzelnes Element.

Ein elektronisches Produkt besteht oft aus vielen ICs (integrierten Schaltkreisen), die miteinander verbunden sind, um eine bestimmte Funktion zu erfüllen. In den 1980er Jahren bestanden Rauchmelder beispielsweise aus Allzweck-ICs, wie Komparatoren, Verstärkern und Reglern. Sie waren riesig und verursachten hohe Kosten für Bauteile und Montage. Mit dem verstärkten Wettbewerb lenkt die Notwendigkeit der Kosteneffizienz und der geringen Größe die Notwendigkeit der Fusion und Integration aller Einzelkomponenten in einen einzigen ASIC, was nicht nur die Größe und die Kosten des Rauchmelders reduziert, sondern auch seine Zuverlässigkeit erhöht.

Gemäß dem Mooreschen Gesetz verdoppelt sich die Anzahl der Transistoren und Gatter alle 18 Monate, und die Dichte pro integriertem Schaltkreis nimmt weiter zu. In den nächsten 15 Jahren wird sich die Technologie noch weiter verbessern, da Parallelisierung, CAD-Tools, Logik und Speicher immer schneller werden.

eInfochips hat mit einem Kunden zusammengearbeitet, der die Entwicklung eines Chips der zweiten Generation mit einer Programmierbarkeit von über 10 Tbps auf der Grundlage eines 7-nm-Technologieknotens plante. Der Kunde war auf der Suche nach einem technischen Partner mit diesem Fachgebiet. Sie können mehr über diesen Fall lesen.

ASIC-Chip-Designs gibt es in drei Varianten

- Vollständig individuelles Design

- Semi-Custom Design

- Programmierbarer ASIC

Vorhersage der VLSI-Entwicklung durch die Semiconductor Industries Association-

![]()

Bildquelle: Semantic Scholar

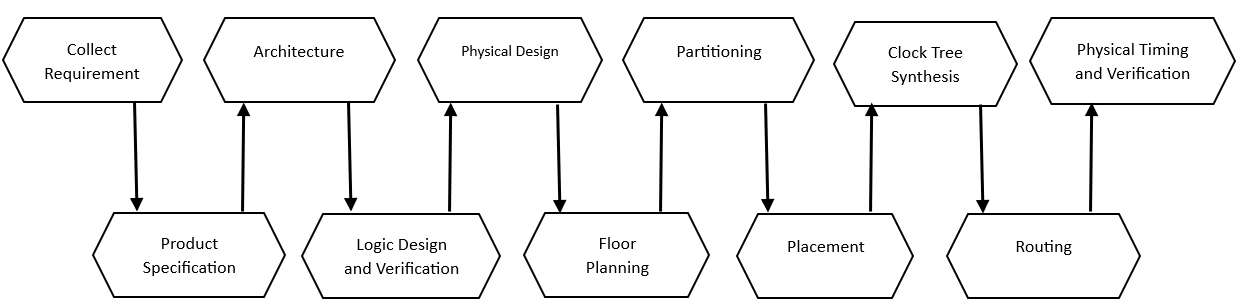

ASIC-Design-Prozess

ASIC-Anforderung

Die Kunden eines Halbleiterunternehmens verwenden den Chip in ihren Endprodukten und Systemen. Die Anforderungen der Kunden stehen bei der Entwicklung eines Chips an erster Stelle. Der erste Schritt besteht darin, die Anforderungen zu erfassen, den Wert des Endprodukts zu ermitteln und die Anzahl der für das Projekt erforderlichen Ressourcen zu bestimmen.

ASIC-Spezifikation

Die ASIC-Spezifikation ist ein Dokument, das die Produktspezifikationen auflistet, bevor man sich auf die Reise der Produktentwicklung begibt. Außerdem wird darin aufgezählt, wie ein Gerät seine Funktionen in verschiedenen Betriebssituationen ausführen sollte. So ist beispielsweise die Phase der Zehntenspezifikation ein wichtiger Teil des Entwurfs- und Entwicklungsprozesses. In einer Zeit, in der die Technologie in allen Lebensbereichen Einzug gehalten hat, erwarten die Kunden neue Designmerkmale, ständige Verbesserungen, Hochgeschwindigkeitsverarbeitung und geringen Stromverbrauch.

Ein Experte für ASIC-Systemdesign hilft dem Kunden bei der Erstellung der Systemarchitektur und -spezifikation. Dieser Prozess dauert etwa zwei bis sechs Wochen, je nach Schwierigkeitsgrad der Anwendungsanforderung. Der Spezifikationsprozess umfasst die folgenden Schritte

- Bewertung der Spezifikation, der Systemschaltpläne und des Blockdiagramms

- Ein besseres Verständnis für jedes Designproblem, jede Herausforderung

- Abschluss einer Entscheidung, die sich auf das Endprodukt bezieht, nicht nur auf ASICs

- Entscheidung darüber, ob für Produkte eine Zertifizierung erforderlich ist, z. B. die Einhaltung von IEC und TS

- Erstellung des ASIC-Blockdiagramms mit seinen Funktionskomponenten, Spezifikation

- Silizium-Integration durch Ermittlung von Kompromissen bei der Architektur auf Leiterplattenebene

ASIC-Architektur

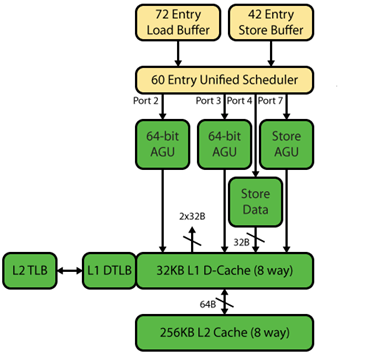

Sobald alle Spezifikationen klar sind, ist es an der Zeit, die ASIC-Leistung in mehrere Leistungsblöcke zu kategorisieren. Die Aufgabe des Architekten besteht darin, die beste Leistung des ASIC-Chips zu erzielen und die Hardwareressourcen zu minimieren, was direkt dazu beiträgt, die Gesamtkosten des Chips innerhalb des zugewiesenen Budgets zu halten. In diesem Kurs definieren die Architekten die Beziehung zwischen den verschiedenen Leistungsblöcken und weisen jedem Block das Zeitbudget zu.

Bild mit freundlicher Genehmigung: Real World Technology

Sobald klar ist, welche Leistungsblöcke benötigt werden, ist es viel einfacher, die kritischen Module zu erkennen und zu überlegen, ob diese IPs aus früheren Projekten wiederverwendet werden sollen oder ob Änderungen an den vorhandenen IPs erforderlich sind.

Was ist Logikdesign und Verifikation?

Dies ist der wichtigste Teil des ASIC-Entwurfsablaufs und umfasst die Codierung des Datenflusses aller Leistungsblöcke in einer Hardwarebeschreibung wie Verilog, VHDL oder Systemverilog. Der Logikentwurf umfasst:

Kombinatorische Logik: Kombinatorische Logik bezieht sich auf boolesche Verknüpfungen wie ODER, UND, NAND, NOR usw. Diese Gatter sind einfach; daher können sie auch zur Durchführung schwieriger digitaler Operationen kombiniert werden.

Sequentielle Elemente: Sequentielle Elemente spielen eine entscheidende Rolle bei der Kombination verschiedener kombinatorischer Logikwolken, die verschiedene Funktionen ausführen, indem sie ihren Ausgang temporär halten. Sequentielle Elemente wie Flip-Flops und Latches werden als Speicherelemente bezeichnet und von einer Koinzidenzschaltung oder einem Steuersignal, dem Taktgeber, verwaltet.

Endliche Zustandsmaschinen (FSMs): Sie sind eine erweiterte Abstraktion der sequentiellen Logik, die sowohl auf Hardware als auch auf Software angewendet werden kann. FSMs modellieren die Reaktion einer digitalen Maschine auf eine Reihe von Eingaben, die eine deterministische Reihe von Ausgaben ergibt, und sind ein wichtiger Baustein für Logikdesigner.

Arithmetische Logikblöcke: Arithmetische Berechnungen sind in der Regel ein Hindernis für die Leistung von Hochleistungs-CPU-Kernen. Sie umfassen Multiplikation, Subtraktion, Addition und Division. Es gibt verschiedene Möglichkeiten, diese Schaltungen auszuführen, die einen Austausch zwischen Leistung, Fläche und Stromverbrauch ermöglichen. Was immer für die Anwendung am besten geeignet ist, kann von den Logikdesignern ausgewählt und für einen oder mehrere Parameter optimiert werden.

Datenpfad-Entwurf: Die Hardwarebeschreibungssprache (HDL) kann den Datenpfadentwurf wie eine Programmiersprache abstrahieren, die von EDA-Tools korrekt übersetzt werden kann.

Analoger Entwurf: ASICs können viele analoge Komponenten enthalten, die als Schnittstelle zur realen Welt dienen und Temperatursensoren, Analog-Digital-Wandler (ADC) und Digital-Analog-Wandler (DAC) umfassen können.

Mit dem Logikentwurf muss das Verifizierungsteam auch einen Verifizierungsplan für die digitalen und analogen Logikkomponenten erstellen. Das Team erstellt praktische Tests, um das Design auf alle möglichen Eckfälle hin zu überprüfen und die korrekte und konsistente Funktionalität mit der Anwendung sicherzustellen. Das Schreiben der RTL-Codierung (Register-Transfer-Level) nimmt 10-20 % der gesamten Design-Zykluszeit in Anspruch, während für die Verifikation 80-90 % der Zeit benötigt werden.

Was ist physikalisches Design?

Der physische Entwurf wird auch als Back-End-Design bezeichnet. Dabei handelt es sich um den Prozess der Umwandlung der bei der Synthese erstellten Gate-Level-Netzliste in praktische ASIC-Hardware. Der Ablauf des physikalischen Entwurfs wird in die folgenden Abschnitte unterteilt

Floorplanning: Beim Floorplanning werden die Funktionsblöcke im Chipbereich platziert, um einen Routingbereich zwischen ihnen zuzuweisen, kritische Strom- und Masseanschlüsse zu arrangieren und über die Lage der Eingangs-/Ausgangs-Pads zu entscheiden. Ein qualitativ hochwertiger Floorplan stabilisiert die Designrestriktionen, um die Gesamtfläche des Chips zu verringern und die Signalroutingkanäle zu verbessern, um das Layout und die Signalleistung zu beruhigen, sowie die relative Platzierung der Funktionsblöcke, um Interferenzen zu verringern und die Signalintegrität zu erhalten.

Partitionierung: Unter Partitionierung versteht man die Aufteilung des Chips in kleine Blöcke. Der Hauptzweck der Partitionierung besteht darin, die Funktionsblöcke für das Routing und die Platzierung einfacher zu gestalten.

Platzierung: Bei der Platzierung wird der Chip in kleinere Blöcke aufgeteilt, indem diese korrekt mit den Standardzellen positioniert werden und sichergestellt wird, dass sich nichts auf dem Chip überlappt. Für die Platzierung gibt es vier Phasen: Pre-Placement, In-Placement und Post-Placement vor und nach der Taktbaumsynthese.

Taktbaum-Synthese

Bild mit freundlicher Genehmigung: System zu ASIC

Die Taktbaumsynthese ist ein Vorgang, der die gleichmäßige Zuordnung von Taktsignalen zu allen sequentiellen Elementen in einem Entwurf bestätigt, um Fehler bei der Taktung zu vermeiden. Die Taktung von Gattern in schnelllebigen Entwürfen unterliegt Fehlern, die dadurch entstehen, dass die Taktflanke nicht genau zu dem Zeitpunkt erscheint, zu dem sie erwartet wird, verglichen mit dem Zeitpunkt, zu dem sie an anderen Teilen der Schaltung erscheint. Dieser Zeitfehler wird als Taktversatz bezeichnet und hängt von mehreren Variablen ab, sowohl im ursprünglichen Entwurf als auch bei der physischen Ausführung.

Verlegung: Beim Routing werden Makros, E/A-Anschlüsse, Stromversorgung, Standardzellen und die Uhr physisch mit Leiterbahnen verbunden. Es wird in zwei Schritte unterteilt: globales und detailliertes Routing.

Physikalische und zeitliche Verifizierung

Die logische Verifikation gewährleistet die korrekte Leistung und die physikalische Verifikation bestätigt das korrekte Layout. Die Zahl der physischen Verifizierungen hat zugenommen und umfasst Design Rule Checks (DRS), Layout Versus Schematic (LVS), Shorts und Floating Nets. Es ist von entscheidender Bedeutung, diese Verstöße Seite an Seite mit dem Platz- und Routenfluss zu verfolgen, um Schluckauf wenige Tage vor dem Tape-Out zu vermeiden.

Abschließende Überlegungen

Wenn Sie den ASIC-Entwurfsprozess sorgfältig durchführen, können Sie enorme Vorteile im Hinblick auf die Senkung der Stückkosten und die Verbesserung der Leistung erzielen. Treten jedoch Fehler auf, steigen die Entwicklungskosten, und der ASIC-Design- und Entwicklungsprozess muss wiederholt werden. Daher ist äußerste Sorgfalt erforderlich, um zu gewährleisten, dass die ASIC-Entwicklung erfolgreich verläuft. eInfochips verfügt über mehr als 25 Jahre Erfahrung in der Unterstützung seiner Kunden beim digitalen und Mixed-Signal-ASIC-Design sowie bei der Entwicklung von FPGA-SoCs für verschiedene Branchen. Wir bieten DFT/DFM-Dienstleistungen, Architekturdefinition und -implementierung, FPGA-zu-ASIC-Konvertierung, Validierung vor dem Silizium und Validierung nach dem Silizium. Um mehr über unsere wichtigsten Angebote und Dienstleistungen zu erfahren , lesen Sie hier und um unser Expertenteam zu kontaktieren , klicken Sie hier.