Dans le monde entier, des équipes d'ingénieurs ont travaillé en coopération pour mettre au point des technologies futuristes avancées dans des ASIC (circuits intégrés à application spécifique) de la taille d'une minute. Cette course passionnante est pleine de défis : trouver des circuits intégrés compacts, plus rapides et plus efficaces pour construire les technologies futures. Dans un rapport publié par Grand View Research, la taille du marché mondial des circuits intégrés à application spécifique (ASIC) a été évaluée à 15,99 milliards USD en 2022, et de 2023 à 2030, il est prévu qu'il se développe à un taux de croissance annuel moyen de 5,9 %.

Circuit intégré à application spécifique (ASIC) : Qu'est-ce que c'est ?

La conception d'un ASIC est un processus de réduction de la taille et du coût d'un circuit électronique, d'un produit ou d'un système. Il s'agit de réduire et d'intégrer un composant unique et ses performances dans un élément individuel.

Un produit électronique combine souvent de nombreux circuits intégrés (CI) qui sont assemblés pour remplir une fonction spécifique. Par exemple, dans les années 1980, les détecteurs de fumée étaient constitués de circuits intégrés à usage commun, tels que des comparateurs, des amplificateurs et des régulateurs. Ils étaient énormes et comportaient beaucoup de composants et de coûts d'assemblage. Avec l'intensification de la concurrence, la nécessité d'un bon rapport coût-efficacité et d'une taille réduite impose la fusion et l'intégration de tous les composants individuels en un seul ASIC, ce qui réduit non seulement la taille et le coût du détecteur de fumée, mais améliore également sa fiabilité.

Selon la loi de Moore, le nombre de transistors et de portes double tous les 18 mois et la densité par circuit intégré augmente. Les 15 prochaines années seront marquées par de nouvelles avancées technologiques grâce à l'accélération de la parallélisation, des outils de CAO, de la logique et de la mémoire.

eInfochips a travaillé avec un client qui prévoyait de concevoir une puce de deuxième génération, avec une programmabilité supérieure à 10 Tbps basée sur un nœud technologique de 7nm. Le client recherchait un partenaire d'ingénierie avec ce domaine d'expertise. Vous pouvez en savoir plus sur ce cas.

Les puces ASIC sont de trois types

- Conception entièrement personnalisée

- Conception semi-personnalisée

- ASIC programmable

Prévision de l'évolution du VLSI par la Semiconductor Industries Association-

![]()

Source de l'image : Semantic Scholar

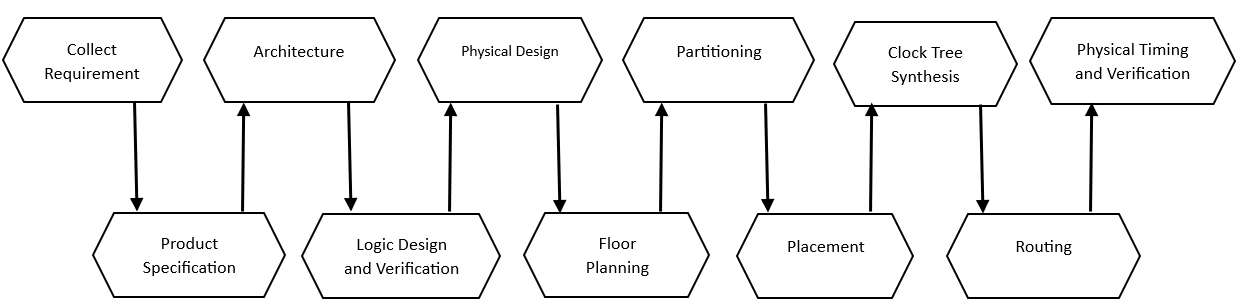

Processus de conception ASIC

Exigence de l'ASIC

Les clients d'une société de semi-conducteurs utilisent la puce dans leurs produits et systèmes finaux. Les exigences des clients sont primordiales lors de la conception d'une puce. La première étape consisterait à rassembler les exigences, à déterminer la valeur du produit final et à évaluer le nombre de ressources nécessaires au projet.

Spécification de l'ASIC

La spécification ASIC est un document qui énumère les spécifications du produit avant de se lancer dans la conception du produit. Il énumère également la manière dont un dispositif doit remplir ses fonctions dans diverses situations opérationnelles. Par exemple, la phase de spécification de la dîme est une partie importante du processus de conception et de développement. Maintenant que la technologie est ancrée dans tous les aspects de la vie, les clients attendent de nouvelles caractéristiques de conception, des améliorations continues, un traitement à grande vitesse et une faible consommation d'énergie.

Un expert en conception de systèmes ASIC aide le client à élaborer l'architecture et les spécifications du système. Ce processus prend entre deux et six semaines, en fonction du degré de difficulté de l'application requise. Le processus de spécification comprend les étapes suivantes

- Évaluation de la spécification, des schémas du système et du diagramme de blocs

- Mieux comprendre les problèmes de conception, les défis à relever, etc.

- Conclure une décision concernant le produit final, et pas seulement les ASIC

- Décider si une certification est nécessaire pour les produits tels que la conformité aux normes IEC et TS

- Création du schéma fonctionnel de l'ASIC avec ses composants fonctionnels, sa spécification

- Intégration du silicium en déterminant les compromis architecturaux au niveau de la carte

Architecture ASIC

Une fois que toutes les spécifications sont claires, il est temps de classer les performances de l'ASIC en plusieurs blocs de performances. Le travail d'un architecte consiste à obtenir les meilleures performances de la puce ASIC et à minimiser les ressources matérielles qui contribuent directement à maintenir le coût global de la puce dans le budget imparti. Dans ce cours, les architectes définissent la relation entre les différents blocs de performance et attribuent le budget temps à chaque bloc.

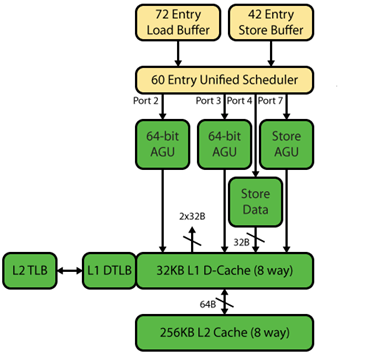

Image Courtesy : Technologie du monde réel

Une fois que les blocs de performance requis sont clairement définis, il est beaucoup plus facile d'identifier les modules critiques et de déterminer s'il faut réutiliser les éléments de propriété intellectuelle des projets précédents ou apporter les modifications nécessaires aux éléments de propriété intellectuelle existants.

Qu'est-ce que la conception et la vérification logiques ?

Il s'agit de la partie la plus importante du processus de conception d'un ASIC, qui comprend le codage du flux de données de tous les blocs de performance dans une description matérielle telle que Verilog, VHDL ou Verilog système. La conception logique comprend

Logique combinatoire : La logique combinatoire fait référence à la combinatoire booléenne telle que OR, AND, NAND, NOR, etc. Ces portes sont faciles à utiliser ; elles peuvent donc être combinées pour effectuer des opérations numériques difficiles.

Éléments séquentiels : Les éléments séquentiels jouent un rôle crucial dans la combinaison de divers nuages logiques combinatoires exécutant différentes fonctions en gardant leur sortie temporaire. Les éléments séquentiels tels que les bascules et les verrous sont appelés éléments de mémoire et sont gérés par un circuit de coïncidence ou un signal de commande appelé horloge.

Machines à états finis (FSM) : Il s'agit d'une abstraction élevée de la logique séquentielle qui peut être appliquée à la fois au matériel et au logiciel. Les FSM modélisent la réaction d'une machine numérique à l'ensemble des entrées, ce qui donne un ensemble déterministe de sorties et constitue un élément de base essentiel pour les concepteurs logiques.

Blocs logiques arithmétiques : Les calculs arithmétiques sont généralement un obstacle à la performance des cœurs d'unités centrales de haute performance. Ils comprennent la multiplication, la soustraction, l'addition et la division. Il existe plusieurs façons d'exécuter ces circuits qui permettent de trouver un compromis entre performance, surface et puissance. Les concepteurs de circuits logiques peuvent choisir celle qui convient le mieux à leur application et l'optimiser pour un ou plusieurs paramètres.

Conception du chemin de données : Le langage de description du matériel (HDL) peut copier de manière abstraite la conception du chemin de données comme un langage de programmation qui peut être traduit correctement par les outils EDA.

Conception analogique : L'ASIC peut comporter de nombreux composants analogiques qui facilitent l'interface avec le monde réel et peuvent inclure des capteurs de température, des convertisseurs analogiques-numériques (ADC) et des convertisseurs numériques-analogiques (DAC).

Avec la conception logique, l'équipe de vérification doit également élaborer un plan de vérification pour les composants logiques numériques et analogiques. L'équipe génère des tests pratiques pour vérifier la conception dans tous les cas de figure possibles et garantir une fonctionnalité correcte et cohérente avec l'application. L'écriture du codage du niveau de transfert de registre (RTL) prend 10 à 20 % de la durée totale du cycle de conception, tandis que les comptes de vérification prennent 80 à 90 % du temps.

Qu'est-ce que la conception physique ?

La conception physique est également connue sous le nom de conception back-end. Il s'agit du processus consistant à transformer la liste de réseaux de niveau de porte produite lors de la synthèse en matériel ASIC pratique. Le flux de conception physique est subdivisé comme suit

Planification de l'étage : Le floorplanning est la procédure qui consiste à placer les blocs fonctionnels dans la zone de la puce afin d'attribuer une zone de routage entre eux, d'organiser l'alimentation critique et la connexion à la terre, et de décider de l'emplacement des tampons d'entrée/sortie. Un plan de qualité stabilise les restrictions de conception afin de réduire la surface totale de la puce et d'améliorer les canaux d'acheminement des signaux afin d'apaiser la disposition et les performances des signaux, ainsi que l'emplacement relatif des blocs fonctionnels afin de réduire les interférences et de maintenir l'intégrité des signaux.

Partitionnement : Le partitionnement est la procédure qui consiste à diviser la puce en petits blocs. L'objectif principal du partitionnement est de construire le bloc fonctionnel plus facilement pour le routage et le placement.

Placement : Le placement est la procédure qui consiste à diviser la puce en blocs plus petits en les positionnant correctement par rapport aux cellules standard, en veillant à ce que rien ne se chevauche sur la puce. Il y a quatre phases pour effectuer le placement : pré-placement, in-placement, et post-placement avant et après la synthèse de l'arbre d'horloge.

Synthèse de l'arbre d'horloge

Image Courtesy : Du système à l'ASIC

La synthèse de l'arbre d'horloge est une opération qui confirme l'attribution uniforme des signaux d'horloge à tous les éléments séquentiels d'une conception afin d'éviter les erreurs liées à la synchronisation de l'horloge. L'horloge des portes dans les conceptions à évolution rapide est sujette à des erreurs qui se produisent parce que le bord de l'horloge n'apparaît pas au moment exact où il est attendu, par rapport au moment où il apparaît dans d'autres parties du circuit. Cette erreur de synchronisation est appelée skew d'horloge et dépend de plusieurs variables, à la fois dans la conception originale et dans l'exécution physique.

Routage : Le routage est une opération qui consiste à attacher physiquement les macros, les ports d'E/S, l'alimentation, les cellules standard et l'horloge à l'aide de traces métalliques. Il est divisé en deux étapes : le routage global et le routage détaillé.

Vérification physique et temporelle

La vérification logique assure une performance précise et la vérification physique certifie une disposition précise. Les contrôles de vérification physique ont augmenté, notamment les vérifications des règles de conception (DRS), la mise en page par rapport au schéma (LVS), les courts-circuits et les réseaux flottants. Il est essentiel de suivre ces violations parallèlement au flux de placement et d'acheminement afin d'éviter tout problème quelques jours avant la sortie.

Réflexions finales

Si le processus de conception d'un ASIC est réalisé avec soin, il est possible d'en tirer d'énormes avantages en termes de réduction du coût unitaire et d'amélioration des performances. Toutefois, si des erreurs se produisent, le coût de développement augmente et il est nécessaire de répéter le processus de conception et de développement de l'ASIC. eInfochips a plus de 25 ans d'expérience dans l'aide à ses clients pour la conception d'ASIC numériques et à signaux mixtes, et le développement de FPGA-SoCs pour différentes industries. Nous offrons des services de DFT/DFM, de définition d'architecture et d'implémentation, de conversion FPGA vers ASIC, de validation pré-silicium et de validation post-silicium. Pour en savoir plus sur nos offres et services clés , lisez ici et pour contacter notre équipe d'experts , cliquez ici.