Heutzutage spielt die Platzierung mehrerer IPs auf einem einzigen Chip die wichtigste Rolle bei der Erfüllung der Anforderungen der System-on-Chip-ASIC-Spezifikation. Meistens haben diese verschiedenen IPs unterschiedliche Taktdomänen.

In diesem Szenario wird die Verwendung von Multi-Clock-Domänen in aufwendigen Designs zum Ausgleich von Scan-Ketten als Einschränkung der Scan-I/O-Ports unerlässlich. Bei der DFT vermeiden wir es in der Regel, verschiedene Taktgeber in derselben Kette zu mischen, aber wenn es eine Einschränkung bei den E/A-Ports gibt, müssen wir Scan-Flops, die von zwei verschiedenen Taktgebern gesteuert werden, in einer Kette zusammenfügen. Ein solches Szenario ist jedoch eine Einladung zu Herausforderungen wie Halteverletzungen und die Generierung von Mustern für Übergangsverzögerungsfehler, um Fehler zwischen Taktdomänen abzudecken.

FALLSTUDIE HERUNTERLADEN

Design für Testbarkeit für einen Hochgeschwindigkeits-Gigabit-Ethernet-Controller für Netzwerke

In diesem Artikel werden die Verwendung von Lock-up Latch und ein Verzögerungstestkonzept für SoC-Bauteile mit mehreren Taktdomänen vorgestellt. Die Schaltung zur Hochgeschwindigkeits-Takterzeugung auf dem Chip ist im SoC implementiert, um teure Testgeräte zu vermeiden. Die Verwendung eines ATE für die Takterzeugung erfordert auch einen Hochgeschwindigkeits-Taktgenerator, um schnelle Taktimpulse für Start und Erfassung zu erzeugen. In der Regel ist ein solcher Hochgeschwindigkeitstaktgenerator in preisgünstigen ATEs nicht verfügbar.

DFT-Herausforderungen

Lassen Sie uns nun über die DFT-Herausforderungen bei der Entwicklung von Multi-Clock-Domains sprechen. Die Verwendung gemischter Takte in derselben Abtastkette würde zu:

- Verletzung der Haltepflicht

- Verringerung des Abdeckungsgrads während der Übergangsverzögerung - ATPG (Automatic Test Pattern Generator)

Lassen Sie uns diese beiden Herausforderungen in Kürze verstehen:

1) Verletzung der Haltezeit

Haltezeit: Die minimale Zeitspanne nach dem Eintreffen der Taktflanke, in der die Daten stabil sein müssen, wird als "Haltezeit" bezeichnet. Mit anderen Worten: Die Daten müssen nach dem Eintreffen der Taktflanke eine gewisse Zeit lang stabil sein, damit sie ordnungsgemäß erfasst werden können. Ein Verstoß in diesem Fall kann dazu führen, dass falsche Daten zwischengespeichert werden, was als "hold violation" bezeichnet wird.

Wir wissen, dass die Daten, die bei der aktuellen Taktflanke erfasst werden sollen, bei der vorherigen Taktflanke von einem anderen Flipflop eingeleitet wurden, während die Daten, die bei der aktuellen Taktflanke eingeleitet werden, bei der nächsten Taktflanke erfasst werden müssen. Die Haltezeit sorgt dafür, dass die bei der aktuellen Taktflanke eingeleiteten Daten nicht bei der aktuellen Taktflanke erfasst werden und die bei der vorherigen Taktflanke eingeleiteten Daten erfasst werden und nicht durch die bei der aktuellen Flanke eingeleiteten Daten gestört werden. Die Haltezeit stellt sicher, dass der aktuelle Zustand des Entwurfs nicht gestört wird.

2) Verringerung des Abdeckungsgrads während der Übergangsverzögerung - ATPG (Automatic Test Pattern Generator)

VERBUNDENER BLOG

DFT-Herausforderungen für phasenverschobene Funktionstaktgeber

SoC-Bauteile verfügen über mehrere funktionale Taktdomänen. Bei einem At-Speed-Test müssen alle Taktdomänen mit ihren eigenen funktionalen Geschwindigkeiten getestet werden. In einem solchen Fall besteht die Lösung darin, dass die Prüfung in einer Taktdomäne nach der anderen erfolgt, um eine Verzögerungsprüfung mit mehreren Taktdomänen durchzuführen.

Dabei kommt es in der Regel vor, dass die Logik zwischen solchen Taktdomänen ungetestet bleibt, was zu einem Anstieg der Musteranzahl und einer geringeren Fehlerabdeckung führt. Das Erreichen einer hohen Fehlerabdeckung während des Tests erweist sich als eine der größten DFT-Herausforderungen für Designs mit mehreren Taktdomänen.

Ansatz zur Lösung von DFT-Herausforderungen

1) Überwindung der Verletzung der Haltepflicht

Zur Überwindung der Hold Violation soll das folgende Szenario untersucht werden:

Wenn alle Scan-Zellen gleichzeitig eine Taktflanke erhalten, treten keine Timing-Verletzungen auf. Wird jedoch eine andere Taktdomäne verwendet, kann es aufgrund von Latenzzeiten in der Taktdomäne zu Halteverletzungen kommen.

Betrachten wir ein Beispiel mit zwei Scan-Flops, die von zwei verschiedenen Taktgebern gesteuert werden.

Wenn die CLK2-Wellenform an FF2 verzögert ist, kann es zu einer Halteverletzung kommen, bei der FF2 fälschlicherweise die Daten des aktuellen Zyklus anstelle der Daten des vorherigen Zyklus erfasst. Abb. 2 zeigt diese Hold-Verletzung für Lead-Edge-Scan-Zellen.

Ein Lock-up-Latch verhindert Halteverletzungen für Scan-Zellen, die Daten mit einer schiefen Taktflanke erfassen könnten. Es handelt sich dabei um eine Latch-Zelle, die zwischen zwei Scan-Zellen eingefügt wird und durch die Inversion des Taktes der vorherigen Scan-Zelle getaktet wird. Abb. 3 zeigt die gleichen zwei Scan-Zellen mit einem zusätzlichen Lock-up-Latch.

Die Lock-up-Latch-Zelle hält die Abtastdaten des vorherigen Zyklus fest, während die Abtastdaten des aktuellen Zyklus erfasst werden, wodurch der Übergang der Ausgangsdaten auf die nächste Flanke des Quellentakts verzögert wird. Abb. 4 zeigt das Lock-up-Timing-Verhalten für dieses Beispiel.

2) Verringerung des Abdeckungsgrads während der Übergangsverzögerung - ATPG (Automatic Test Pattern Generator)

Die Lösung für dieses Problem ist die "Synchronous OCC"-Technik. Lassen Sie uns tiefer eintauchen.

Die Technik der synchronen On-Chip-Takterzeugung soll die Anzahl der Testvektoren reduzieren und die Testqualität erhöhen. Ein synchroner OCC kann Taktimpulse zwischen jeder synchronen Taktdomäne erzeugen, die den OCC durchläuft (ein Impuls pro Domäne), um Fehler zwischen den Taktdomänen abzudecken. Die Bitwerte der OCC-Schiebekette werden verwendet, um die gezielten Taktimpulse (Start und Erfassung) für jede Taktdomäne zu erzeugen.

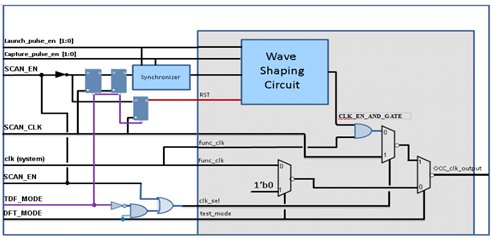

Abb. 5 unten zeigt ein Szenario, in dem der synchrone OCC zwei verschiedene Taktgeber synchronisiert, um das Muster des Übergangsverzögerungs-Fehlermodells zu erzeugen.

Hier zeigt launch_en [1:0] das Startbit von 2 verschiedenen OCC an, ähnlich wie capture_en[1:0]. Durch die Anwendung des konstanten Werts 1 auf Shiften können wir Start- und Erfassungsimpulse von der Impulsformungsschaltung basierend auf dem Start- und Erfassungsbit erhalten.

DFT Tool - DAeRT : Dft Automated execution and Reporting Tool

DAeRT ermöglicht es, eine ~100%ige Testbarkeit für ASIC-Designs zu erreichen. Es unterstützt verschiedene DFT-Methoden, beginnend mit IJTAG/JTAG, MBIST, Scan, ATPG, Pattern Validation, Test Timing Analysis und Post-Si-Validierung.

Wie Sync OCC funktioniert

Grundsätzlich wird Sync OCC verwendet, um während des Erfassungsvorgangs Start- und Erfassungsimpulse aus zwei verschiedenen Taktbereichen zu erzeugen, wie in Abb. 6 gezeigt.

Sehen wir uns das im Detail an:

- Übertragen Sie den Wert 1 auf TDF_MODE und DFT_MODE. Jetzt ist clk_sel abhängig von SCAN_EN. Wenn also SCAN_EN=1 (Shift-Operation) ist, wird SCAN_CLK gewählt, während SCAN_EN=0 (Capture-Operation) func_clk wählt.

- Betrachten wir nun SCAN_EN=0 für den Erfassungsvorgang. Nach zwei Taktzyklen von SCAN_CLK wird der Synchronisierschaltkreis angesteuert.

- Hier beziehen sich Launch_pulse_en[0] und Capture_pulse_en[0] auf OCC-1, während sich Launch_pulse_en[1] und Capture_pulse_en[1] auf OCC-2 beziehen.

- Der Synchronisierschaltkreis erzeugt den Wert 1 an Launch_pulse_en[0] und Capture_pulse_en[1], so dass der Ausgang des Wellenformungsschaltkreises für zwei Funktionstaktzyklen den Wert 1 hat.

- Da SCAN_EN=0, TDF_MODE=1 und DFT_MODE=1, erhalten wir den Startimpuls und den Erfassungsimpuls als Ausgabe am OCC_clk_output.

Bitte prüfen Sie die in Abb. 7 gezeigte Wellenform

ATPG-Einrichtung

1. Write Clocking Verfahren für Sync OCC

Nehmen wir einen Entwurf mit 71 OCC. In einem solchen Fall enthält die OCC-Schiebekette 142(71*2) Flipflops (wobei 2 für das Startbit und das Fangbit jedes OCC steht). Die Taktprozedur für diese Kette ist wie folgt:

In diesem Beispiel hat CLKIR 142 Bits; wenn wir es auf 1 setzen, können wir Start- und Fangimpulse vom jeweiligen OCC erhalten.

Auf der Grundlage der CLKIR-Sequenz können wir den Startimpuls von E_OCC und den Fangimpuls von C_OCC erhalten.

2. Fügen Sie den folgenden Befehl zum Skript TMAX hinzu

Schlussfolgerung

Für ASICs der nächsten Generation mit mehreren IPs, die in unterschiedlichen Taktbereichen arbeiten, spielt die On-Chip-Takterzeugungsschaltung eine Schlüsselrolle. Die in diesem Artikel beschriebene Methode hilft bei der Verbesserung der Fehlerabdeckung mit einer minimalen Anzahl von Mustern. Sie hilft auch bei der Überprüfung von On-Hold-Verletzungen, da wir eine Zyklusverzögerung zwischen Start- und Erfassungsimpuls bestätigen können.

Bauen Sie Ihr SoC der nächsten Generation mit dem DFT Engagement-Modell

Autoren

Ramesh Devani, Mayank Kapadiya, Piyush Chaniyara und Khushali Dudhagara