今日、1つのチップ上に複数のIPを配置することは、システム・オン・チップASICの仕様要件を満たす上で最も重要な役割を果たしている。ほとんどの場合、これらの異なるIPは異なるクロック・ドメインを持ちます。

このシナリオでは、スキャンI/Oポートの制限があるため、精巧な設計ではスキャンチェーンのバランスを取るためにマルチクロックドメインの使用が不可欠になっています。主にDFTでは、同じチェーンに異なるクロックが混在することは避けますが、I/Oポートに制約がある場合は、1つのチェーンに2つの異なるクロックで駆動されるスキャン・フロップをつなぎ合わせる必要があります。しかし、このようなシナリオは、ホールド違反や、クロック・ドメイン間の故障をカバーするための遷移遅延故障のパターン生成といった課題を招くことになる。

本稿では、複数のクロック・ドメインを持つSoCデバイスのためのロックアップ・ラッチと遅延テストのコンセプトを紹介する。高価なテスト装置を避けるため、SoCには高速オンチップ・クロック生成回路が実装されている。また、ATEでクロッキングを行う場合、高速クロックジェネレータが必要となる。通常、このような高速クロック・ジェネレーターは低価格のATEでは利用できない。

DFTの課題

次に、マルチクロック・ドメイン設計におけるDFTの課題について説明しよう。同じスキャン・チェーンでクロックを混在させると、次のようなことが起こります:

- ホールド違反

- 移行遅延中のカバレッジ低下-ATPG(自動テストパターン生成器)

この2つの課題を簡単に理解しよう:

1) ホールド時間違反

ホールド・タイム:クロック・エッジ到着後、データが安定していなければならない最小の時間を「ホールド・タイム」と呼ぶ。つまり、クロック・エッジ到着後、データが正しく取り込まれるように、ある程度の時間データが安定している必要がある。これに違反すると、誤ったデータがラッチされる可能性があり、これをホールド違反という。

現在のクロックエッジで捕捉されるべきデータは他のフリップフロップによって前のクロックエッジで立ち上げられたことが分かっており、現在のクロックエッジで立ち上げられたデータは次のクロックエッジで捕捉されなければならない。ホールド タイムは、現在のクロック エッジで立ち上げられたデータが現在のクロック エッジでキャプチャされないようにし、前のクロック エッジで立ち上げられたデータがキャプチャされ、現在のエッジで立ち上げられたデータによって妨害されないようにします。ホールド・タイムは、デザインの現在の状態が乱されないようにする。

2) トランジションディレイ時のカバレッジ低下-ATPG(自動テストパターンジェネレーター)

関連ブログ

SoCデバイスは複数の機能クロックドメインを実装している。アットスピード・テストでは、すべてのクロック・ドメインをそれぞれの機能速度でテストしなければならない。このような場合、マルチクロックドメイン遅延テストのために、テストは1つのクロックドメインで次々に行われることが解決策となる。

一般的に、このようなクロック・ドメイン間のロジックは未テストのままとなり、パターン数の増加やカバレッジの低下というペナルティが生じます。テスト中に高いフォルト・カバレッジを達成することは、複数のクロック・ドメインを持つ設計におけるDFTの最大の課題の1つです。

DFTの課題を解決するアプローチ

1) ホールド違反の克服

ホールド違反を克服するために、以下のシナリオを考えてみよう:

すべてのスキャン・セルが同時にクロック・エッジを受信すれば、タイミング違反は発生しない。しかし、クロック・ドメインのレイテンシが原因で異なるクロック・ドメインが使用されると、ホールド違反が発生する可能性がある。

2つの異なるクロックで駆動される2つのスキャン・フロップの例を考えてみよう。

FF2のCLK2波形が遅延すると、FF2が前サイクルのデータではなく現サイクルのデータを誤って取り込むホールド違反が発生する可能性がある。図2は、リーディング・エッジ・スキャン・セルにおけるこのホールド違反を示している。

ロックアップ・ラッチは、スキューされたクロック・エッジを使ってデータを取り込むスキャン・セルのホールド違反を防ぐ。これは、2つのスキャン・セルの間に挿入され、前のスキャン・セルのクロックの反転によってクロックされるラッチ・セルである。図3は、同じ2つのスキャン・セルにロックアップ・ラッチを追加したものである。

ロックアップ・ラッチ・セルは、現在のサイクルのスキャン・データがキャプチャされる間、前のサイクルのスキャン・データを保持することで動作し、出力データの遷移をソース・クロックの次のエッジまで効果的に遅らせる。図4は、この例のロックアップ・タイミングの動作を示している。

2) トランジションディレイ時のカバレッジ低下-ATPG(自動テストパターンジェネレーター)

この問題を解決するのが「同期OCC」テクニックだ。さらに深く掘り下げてみよう。

同期オンチップ・クロック生成技術は、テスト・ベクタ数を減らし、テスト品質を向上させることを意図している。同期OCC は、OCC を通過する各同期 ク ロ ッ ク ド メ イ ン間で ク ロ ッ ク パルスを生成す る こ と がで き( ド メ イ ンご と に1 パルス) 、 ク ロ ッ ク ド メ イ ン間の故障を カ バーで き ます。OCC シフ ト チェーンのビ ッ ト 値は、 各 ク ロ ッ ク ド メ イ ンの タ ーゲ ッ ト ク ロ ッ ク パルス( 発進お よ びキ ャ プチ ャ) を生成す る ために使用 さ れます。

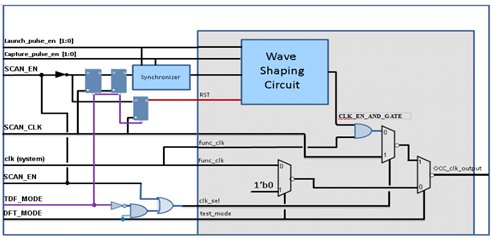

下の図5は、同期OCCが遷移遅延故障モデルのパターンを生成するために2つの異なるクロックを同期させるシナリオを示している。

launch_en[1:0]は capture_en[1:0]と同様に2つの異なる OCC からの発射ビットを示す。shiftenに定数1の値を加えることで、発射ビットと捕獲ビットに基づいたパルス整形回路から発射パルスと捕獲パルスを得ることができる。

DFTツール - DAeRT : Dft自動実行・報告ツール

DAeRTは、ASICデザインのテスト容易性を〜100%達成することを可能にします。IJTAG/JTAG、MBIST、スキャン、ATPG、パターン・バリデーション、テスト・タイミング解析、ポストSiバリデーションに始まる様々なDFT手法をサポートしています。

シンクOCCの仕組み

基本的に、Sync OCCは、図6に示すように、キャプチャ動作中に2つの異なるクロック・ドメインから発進パルスとキャプチャ・パルスを生成するために使用される。

詳しく見てみよう:

- TDF_MODE と DFT_MODE に値 1 を適用する。これで clk_sel は SCAN_EN に依存するようになります。つまり、SCAN_EN=1(シフト動作)の場合はSCAN_CLKが選択され、SCAN_EN=0(キャプチャ動作)の場合はfunc_clkが選択されます。

- ここで、SCAN_EN=0でキャプチャ動作を行うと考える。SCAN_CLKの2クロック後に同期回路が駆動される。

- ここで Launch_pulse_en[0]と Capture_pulse_en[0]は OCC-1 に関連し、Launch_pulse_en[1]と Capture_pulse_en[1]は OCC-2 に関連する。

- 同期回路は、波形整形回路の出力が2機能クロック・サイクルの間1となるようにLaunch_pulse_en[0]とCapture_pulse_en[1]に1を生成する。

- SCAN_EN=0、TDF_MODE=1、DFT_MODE=1であるため、OCC_clk_outputには発射パルスと捕獲パルスが出力される。

図7の波形をご確認ください。

ATPGセットアップ

1.同期 OCC の書き込みクロッキング手順

71 個の OCC を持つデザインを考える。この場合、OCCシフト・チェーンには142(71*2)個のフリップフロップが含まれる。この場合のクロッキング手順は次のようになる:

この例では、CLKIRは142ビットである。これを1に設定することで、それぞれのOCCから発進パルスと捕捉パルスを得ることができる。

CLKIRシーケンスに基づき、E_OCCから発射パルスを、C_OCCから捕獲パルスを得ることができる。

2.TMAXスクリプトに以下のコマンドを追加する。

結論

異なるクロック・ドメインで機能する複数のIPを持つ次世代ASIC SoCでは、オンチップ・クロック生成回路が重要な役割を果たす。本稿で説明する手法は、最小限のパターン数でフォールト・カバレッジを向上させるのに役立つ。また、起動とキャプチャパルス間の1サイクル遅延を確認できるため、オンホールド違反のチェックにも役立ちます。

DFTのエンゲージメントモデルで次世代SoCを構築する

著者紹介

ラメッシュ・デヴァーニ、マヤンク・カパディヤ、ピユシュ・チャニヤラ、クシャリー・ドゥダガラ