# TMDSEVM6474L / TMDSEVM6474LE Technical Reference Manual Version 2.0

Literature Number: SPRUGX2 Revised March 2011

Cenfochips The Solutions People

TEXAS INSTRUMENTS

Document Copyright Publication Title: TMDSEVM6474L / TMDSEVM6474LE Technical Reference Manual.

All Rights Reserved. Reproduction, adaptation, or translation without prior written permission is prohibited, except as allowed under the copyright laws.

#### EVALUATION BOARD/KIT/MODULE (EVM) WARNINGS, RESTRICTIONS AND DISCLAIMER

#### Not for Diagnostic Use: For Feasibility Evaluation Only in Laboratory/Development Environments

The EVM may not be used for diagnostic purposes.

This EVM is intended solely for evaluation and development purposes. It is not intended for use and may not be used as all or part of an end equipment product.

This EVM should be used solely by qualified engineers and technicians who are familiar with the risks associated with handling electrical and mechanical components, systems and subsystems.

#### Your Obligations and Responsibilities

Please consult the EVM documentation, including but not limited to any user guides, set up guides or getting started guides and other warnings prior to using the EVM. Any use of the EVM outside of the specified operating range may cause danger to the users and/or produce unintended results, inaccurate operation, and permanent damage to the EVM and associated electronics. You acknowledge and agree that:

You are responsible for compliance with all applicable Federal, State and local regulatory requirements (including but not limited to Food and Drug Administration regulations, UL, CSA, VDE, CE, RoHS and WEEE,) that relate to your use (and that of your employees, contractors or designees) of the EVM for evaluation, testing and other purposes.

You are responsible for the safety of you and your employees and contractors when using or handling the EVM. Further, you are responsible for ensuring that any contacts or interfaces between the EVM and any human body are designed to be safe and to avoid the risk of electrical shock.

You will defend, indemnify and hold TI, its licensors and their representatives harmless from and against any and all claims, damages, losses, expenses, costs and liabilities (collectively, "Claims") arising out of or in connection with any use of the EVM that is not in accordance with the terms of this agreement. This obligation shall apply whether Claims arise under the law of tort or contract or any other legal theory, and even if the EVM fails to perform as described or expected.

#### Warning

The EVM board may get very hot during use. Specifically, the DSP, its heat sink and power supply circuits all heat up during operation. This will not harm the EVM. Use care when touching the unit when operating or allow it to cool after use before handling. If unit is operated in an environment that limits free air flow, a fan may be needed.

# Preface

#### About this Document

This document is a Technical Reference Manual for the TMS320C6474 Lite EVM designed and developed by elnfochips Limited for Texas Instruments, Inc.

#### **Notational Conventions**

This document uses the following conventions:

Program listings, program examples, and interactive displays are shown in a mono-spaced font. Examples use **bold** for emphasis, and interactive displays use bold to distinguish commands that you enter from items that the system displays (such as prompts, command output, error messages, etc.).

Square brackets ([and]) identify an optional parameter. If you use an optional parameter, you specify the information within the brackets. Unless the square brackets are in a bold typeface, do not enter the brackets themselves.

<u>Underlined, italicized non-bold</u> text in a command is used to mark place holder text that should be replaced by the appropriate value for the user's configuration.

SPRUGX2 - Revised March 2011

# Trademarks

The Texas Instruments logo and Texas Instruments are registered trademarks of Texas Instruments. Trademarks of Texas Instruments include: TI, XDS, Code Composer, Code Composer Studio, Probe Point, Code Explorer, DSP/BIOS, RTDX, Online DSP Lab, TMS320, TMS320C54x, TMS320C55x, TMS320C62x, TMS320C64x, TMS320C67x, TMS320C5000, and TMS320C6000.

MicroTCA and AMC (or AdvancedMC) are trademarks of PICMG.

All other brand, product names, and service names are trademarks or registered trademarks of their respective companies or organizations.

SPRUGX2 - Revised March 2011

# **Document Revision History**

| Release | Chapter | Description of Change     |

|---------|---------|---------------------------|

| 1.0     | All     | First Draft               |

| 2.0     | All     | Updated for TMDSEVM6474LE |

|         |         |                           |

|         |         |                           |

|         |         |                           |

|         |         |                           |

## Acronyms

| Acronym           | Description                                         |

|-------------------|-----------------------------------------------------|

| AMC or AdvancedMC | Advanced Mezzanine Card                             |

| AIF               | Antenna Interface                                   |

| CCS               | Code Composer Studio                                |

| DDR2              | Double Data Rate 2 Interface                        |

| DIP               | Dual-In-Line Package                                |

| DSP               | Digital Signal Processor                            |

| DTC               | Debug and Trace Controller                          |

| DTE               | Data Terminal Equipment                             |

| EEPROM            | Electrically Erasable Programmable Read Only Memory |

| EMAC              | Ethernet Media Access Controller                    |

| EMIF              | External Memory Interface                           |

| EVM               | Evaluation Module                                   |

| FPGA              | Field Programmable Gate Array                       |

| FSYNC             | Frame Synchronization                               |

| HPI               | Host Port Interface                                 |

| HPI DC            | Host Port Interface Daughter Card                   |

| 12C               | Inter Integrated Circuit                            |

| IPMB              | Intelligent Platform Management Bus                 |

| IPMI              | Intelligent Platform Management Interface           |

| JTAG              | Joint Test Action Group                             |

| LED               | Light Emitting Diode                                |

| McBSP             | Multi Channel Buffered Serial Port                  |

| MCH               | MicroTCA Carrier Hub                                |

| MTCA or MicroTCA  | Micro Telecommunication Computing Architecture      |

| MMC               | Module Management Controller                        |

| NU                | Not Used (Not Assembled)                            |

| PICMG®            | PCI Industrial Computer Manufacturers Group         |

| SDRAM             | Synchronous Dynamic Random Access Memory            |

| SERDES            | Serializer-Deserializer                             |

| SGMII             | Serial Gigabit Media Independent Interface          |

| SRIO              | Serial RapidIO                                      |

| UART              | Universal Asynchronous Receiver/Transmitter         |

| USB               | Universal Serial Bus                                |

| XDS560v2          | Texas Instruments' System Trace Emulator            |

# **Table of Contents**

| 1. 0    | VERVIEW                                              | 10 |

|---------|------------------------------------------------------|----|

| 1.1     | KEY FEATURES                                         | 10 |

| 1.2     | FUNCTIONAL OVERVIEW                                  | 11 |

| 1.3     | BASIC OPERATION                                      | 13 |

| 1.4     | POWER SUPPLY                                         | 14 |

| 2. IN   | TRODUCTION TO THE C6474 LITE EVM BOARD               | 15 |

| 2.1     | MEMORY MAP                                           | 15 |

| 2.2     | EVM BOOT MODE AND BOOT CONFIGURATION SWITCH SETTINGS | 16 |

| 2.3     | CLOCK CONFIGURATION                                  | 16 |

| 2.4     | BOARD REVISION ID                                    | 17 |

| 2.5     | JTAG - EMULATION OVERVIEW                            | 18 |

| 2.5.1   | JTAG – TMDSEVM6474L                                  |    |

| 2.5.2   | JTAG – TMDSEVM6474LE                                 | 19 |

| 2.5.2.1 | XDS560V2 MEZZANINE EMULATOR BOOTING                  | 19 |

| 2.6     | CLOCK DOMAINS                                        | 20 |

| 2.7     | I2C BOOT EEPROM                                      | 20 |

| 2.8     | FPGA                                                 | 21 |

| 2.9     | ETHERNET SWITCH                                      | 22 |

| 2.10    | SERIAL RAPIDIO (SRIO) INTERFACE                      | 22 |

| 2.11    | ANTENNA INTERFACES                                   | 23 |

| 2.12    | UART INTERFACE                                       | 23 |

| 2.13    | MODULE MANAGEMENT CONTROLLER (MMC) FOR IPMI          | 24 |

| 2.14    | ADDITIONAL HEADERS                                   | 24 |

| 3. F    | PGA FUNCTIONAL SPECIFICATION                         | 25 |

| 3.1     | FPGA MODES                                           | 25 |

| 3.2     | FPGA – DSP COMMUNICATION SIGNALS                     | 26 |

| 3.3     | FPGA MEMORY MAP                                      | 27 |

| 3.4     | FPGA CONFIGURATION REGISTERS                         | 28 |

| 3.5     | FPGA-DSP COMMUNICATION PROTOCOL IN FPGA NORMAL MODE  | 29 |

| 3.6     | SEQUENCE OF OPERATION                                | 30 |

| 3.6.1   | BOOT SEQUENCE – POWER-ON (COLD) RESET                | 30 |

| 3.6.2   | BOOT SEQUENCE – WARM RESET                           | 31 |

|         |                                                      |    |

### **Technical Reference Manual**

SPRUGX2 - Revised March 2011

### TMDSEVM6474L TMDSEVM6474LE

| 4.    | EVM BOARD PHYSICAL SPECIFICATIONS                   |    |

|-------|-----------------------------------------------------|----|

| 4.1   | BOARD LAYOUT                                        | 32 |

| 4.2   | CONNECTOR INDEX                                     |    |

| 4.2.1 | J1, AMC EDGE CONNECTOR                              | 34 |

| 4.2.2 | J2, ETHERNET CONNECTOR                              | 36 |

| 4.2.3 | J3, DSP JTAG CONNECTOR                              |    |

| 4.2.4 | J4, MSP430 RESET 2-PIN CONNECTOR                    |    |

| 4.2.5 | J5, MSP430 POWER SELECTION 3-PIN CONNECTOR          |    |

| 4.2.6 | J6, MSP430 JTAG CONNECTOR                           |    |

| 4.2.7 | J8, POWER INPUT JACK CONNECTOR                      |    |

| 4.2.8 | J9, MINI-B USB CONNECTOR                            |    |

| 4.2.9 | J10, UART 3-PIN CONNECTOR                           |    |

| 4.2.1 | J11, GPIO MCBSP, I2C, UART AND TIMER TEST CONNECTOR | 40 |

| 4.2.1 | 1 J12, FPGA JTAG CONNECTOR                          | 41 |

| 4.2.1 | 2 J13, UART PATH SELECT CONNECTOR                   | 41 |

| 4.2.1 | 3 J1, MINI-AB USB CONNECTOR – IN TMDSEVM6474LE ONLY | 41 |

| 4.3   | SWITCHES                                            | 42 |

| 4.3.1 | SW1, COLD RESET                                     | 42 |

| 4.3.2 | SW2, WARM RESET                                     | 42 |

| 4.3.3 | SW3, DSP CONFIGURATIONS                             | 43 |

| 4.3.4 | SW4, DSP BOOT MODE                                  | 44 |

| 4.4   | TEST POINTS                                         | 45 |

| 4.5   | SYSTEM LEDS                                         | 46 |

# List of Figures

| FIGURE 1.1: BLOCK DIAGRAM OF TMDSEVM6474L                   | 11 |

|-------------------------------------------------------------|----|

| FIGURE 1.2: BLOCK DIAGRAM OF TMDSEVM6474LE                  | 12 |

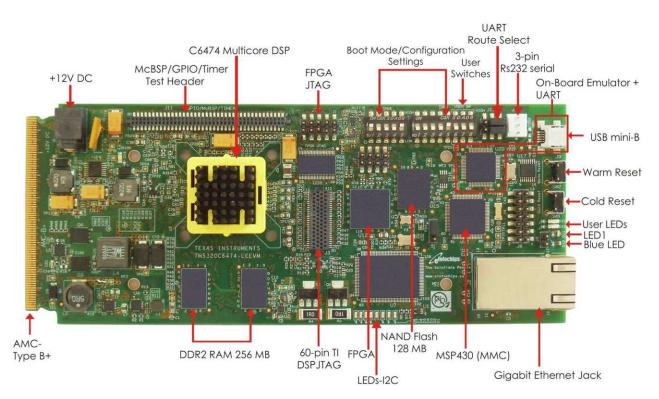

| FIGURE 1.3: TMDSEVM6474L                                    |    |

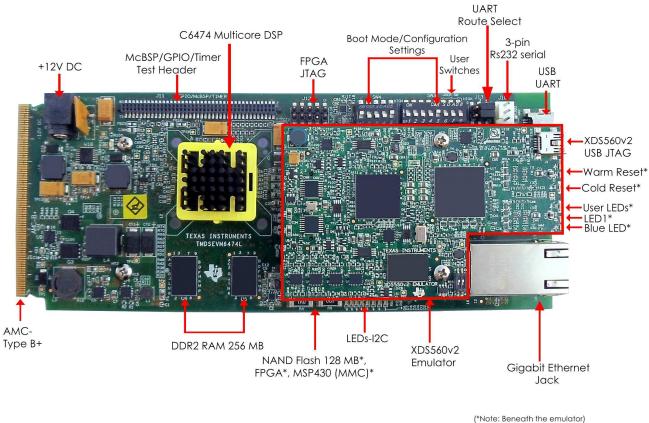

| FIGURE 1.4: TMDSEVM6474LE                                   |    |

| FIGURE 2.1: EVM BOARD REVISION                              |    |

| FIGURE 2.2: TMDSEVM6474L JTAG EMULATION                     |    |

| FIGURE 2.3: TMDSEVM6474LE JTAG EMULATION                    | 19 |

| FIGURE 2.4: C6474 LITE EVM CLOCK DOMAINS                    | 20 |

| FIGURE 2.5: C6474 LITE EVM FPGA CONNECTIONS                 | 21 |

| FIGURE 2.6: C6474 LITE EVM ETHERNET SWITCH ROUTING          | 22 |

| FIGURE 2.7: C6474 LITE EVM SRIO PORT CONNECTIONS            |    |

| FIGURE 2.8: C6474 LITE EVM AIF PORT CONNECTIONS             |    |

| FIGURE 2.9: C6474 LITE EVM UART CONNECTIONS                 |    |

| FIGURE 2.10: C6474 LITE EVM MMC CONNECTIONS FOR IPMI        |    |

| PROCEDURE 3-1: ADDRESS CYCLE INITIATION BY DSP              |    |

| PROCEDURE 3-2: WRITE CYCLE INITIATION BY DSP                |    |

| PROCEDURE 3-3: READ CYCLE INITIATION BY DSP                 | 30 |

| PROCEDURE 3-1: POWER ON RESET                               |    |

| PROCEDURE 3-1: WARM RESET                                   |    |

| FIGURE 4.1: C6474 LITE EVM BOARD ASSEMBLY LAYOUT – TOP VIEW | -  |

| FIGURE 4.2: C6474 LITE EVM BOARD LAYOUT – BOTTOM VIEW       |    |

| FIGURE 4.3: SW3 DEFAULT SETTINGS                            |    |

| FIGURE 4.4: SW4 DEFAULT SETTINGS                            |    |

| FIGURE 4.5: BOARD TEST POINTS <sup>[5]</sup>                |    |

| FIGURE 4.6: TMS320C6474 BOARD LEDS                          |    |

| FIGURE 4.7: TMDSEVM6474LE BOARD ADDITIONAL LEDS             | 47 |

# **List of Tables**

| TABLE 1: TMS320C6474 MEMORY MAP                     | 15 |

|-----------------------------------------------------|----|

| TABLE 2: CLOCK CONFIGURATIONS                       |    |

| TABLE 3: PCA/PCB REVISION DESCRIPTION               |    |

| TABLE 4: GPIO PIN MAPPING IN NORMAL MODE            |    |

| TABLE 5: GPIO PIN MAPPING IN NAND PASS THROUGH MODE |    |

| TABLE 6: FPGA MEMORY MAP                            | 27 |

| TABLE 7: FPGA CONFIGURATION REGISTERS SET           |    |

| TABLE 8: TMS320C6474 BOARD CONNECTORS               |    |

| TABLE 9: AMC EDGE CONNECTOR                         |    |

| TABLE 10: ETHERNET CONNECTOR PIN OUT                |    |

| TABLE 11: DSP JTAG CONNECTOR PIN OUT                |    |

| TABLE 12: MSP RESET CONNECTOR PIN OUT               |    |

| TABLE 13: MSP430 POWER SELECTION CONNECTOR PIN OUT  |    |

| TABLE 14: MSP430 JTAG CONNECTOR PIN OUT             |    |

| TABLE 15: POWER INPUT JACK CONNECTOR PIN OUT        | 39 |

|                                                     |    |

### Technical Reference Manual

| TABLE 16: MINI-B USB CONNECTOR PIN OUT                    | 30 |

|-----------------------------------------------------------|----|

|                                                           |    |

| TABLE 17: UART CONNECTOR PIN OUT                          | 39 |

| TABLE 18: GPIO, McBSP, I2C, UART AND TIMER TEST CONNECTOR | 40 |

| TABLE 19: FPGA JTAG CONNECTOR PIN OUT                     | 41 |

| TABLE 20: UART PATH SELECT CONNECTOR PIN OUT              | 41 |

| TABLE 21: MINI-B USB CONNECTOR PIN OUT                    | 41 |

| TABLE 22: C6474 LITE EVM BOARD SWITCHES                   | 42 |

| TABLE 23: SW3, DSP CONFIGURATION SWITCH                   | 43 |

| TABLE 24: SW4, DSP BOOT MODE SELECTION SWITCH             |    |

| TABLE 25: C6474 LITE EVM BOARD TEST POINTS                | 45 |

| TABLE 26: TMS320C6474 BOARD LEDS                          |    |

| TABLE 27: TMDSEVM6474LE BOARD ADDITIONAL LEDS             |    |

#### 1. Overview

This chapter provides an overview of the C6474 Lite EVM along with the key features and block diagram.

- 1.1 Key Features

- 1.2 Functional Overview

- 1.3 Basic Operation

- 1.4 Power Supply

## 1.1 Key Features

The C6474 Lite EVM is a high performance, cost-efficient, standalone development platform that enables users to evaluate and develop applications for the Texas Instruments' Multicore TMS320C6474 Digital Signal Processor (DSP). The Evaluation Module (EVM) also serves as a hardware reference design platform for the TMS320C6474 DSP. The EVM's form-factor is equivalent to a single-wide PICMG® AMC.0 R2.0 AdvancedMC module.

TMDSEVM6474L comes with an onboard XDS100 emulator. TMDSEVM6474LE comes with an integrated, high speed, system trace capable XDS560v2\_Mezzanine emulator.

Schematics, code examples and application notes are available, to ease the hardware development process and to reduce the time to market.

The key features of the C6474 Lite EVM are:

- Texas Instruments' Fixed-Point Multicore (3 C64x+ Cores) DSP TMS320C6474

- 256 Mbytes of DDR2 Memory

- 128 Mbytes of NAND Flash

- One Gigabit Ethernet port supporting 10/100/1000 Mbps data-rate

- 170 pin B+ style AMC Interface

- I2C EEPROM for booting

- 2 User LEDs and 3 User Switches

- 8 I2C controlled LEDs

- RS232 Serial interface on 3-Pin header or UART over mini-USB connector

- GPIO, McBSP, Timer, FSYNC, UART and I2C signals on 80-pin test header

- On Board FPGA (Actel's ProASIC 3) for DSP boot-strapping and NAND Flash interface

- On-Board XDS100 type Emulation using USB 2.0 interface<sup>[7]</sup>

- TI 60-Pin JTAG header to support External Emulator<sup>[1]</sup>

- High Speed Integrated XDS560v2 Mezzanine Emulator<sup>[2]</sup>

- Module Management Controller (MMC) for Intelligent Platform Management Interface (IPMI)

- Powered by DC power-brick adaptor (12V/2.5A) or AMC Carrier back-plane

- AMC like form factor

Note: [1] - Available in TMDSEVM6474L only [2] - Available in TMDSEVM6474LE only

### 1.2 Functional Overview

The C6474 Lite EVM contains single TMS320C6474 fixed point Digital Signal Processor. TMS320C6474 device is based on the third-generation high-performance, advanced VelociTI<sup>™</sup> very-long-instruction-word (VLIW) architecture, making these DSPs an excellent choice for applications including video and telecom infrastructure, imaging/medical, and wireless infrastructure (WI). The C64x+ devices are upward code-compatible from previous devices that are part of the C6000<sup>™</sup> DSP platform.

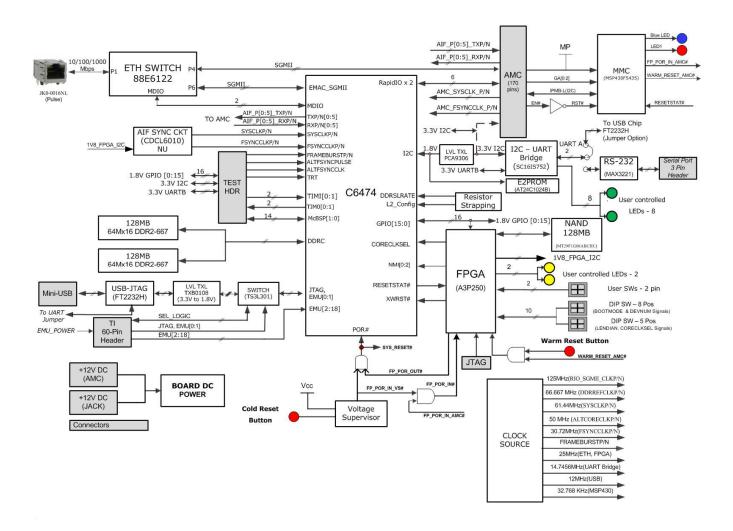

The functional block diagram of TMDSEVM6474L is shown in figure 1.1:

Figure 1.1: Block Diagram of TMDSEVM6474L

SPRUGX2 - Revised March 2011

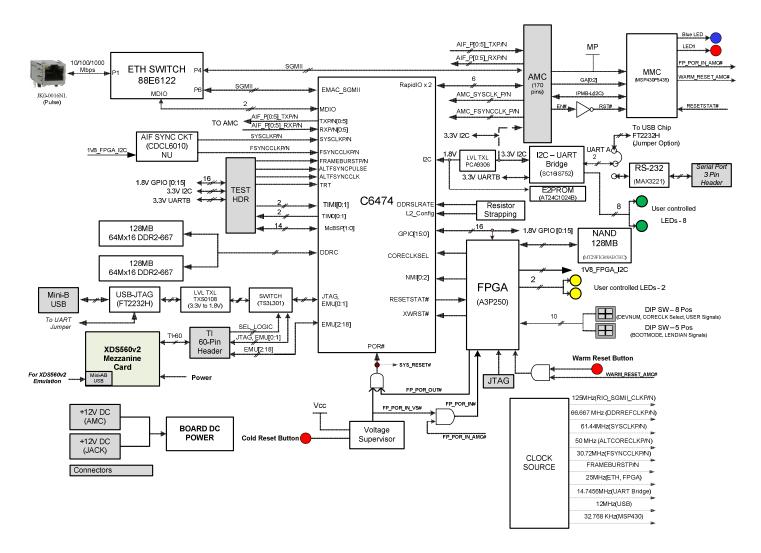

#### The functional block diagram of TMDSEVM6474LE is shown in figure 1.2:

Figure 1.2: Block Diagram of TMDSEVM6474LE

### 1.3 Basic Operation

The C6474 Lite EVM platform is designed to work with TI's Code Composer Studio version 4 (CCSv4) development environment and is shipped with the latest version with all necessary emulation drivers. For TMDSEVM6474L, CCSv4 interfaces with the board via on-board emulation circuitry using the USB cable supplied along with this EVM or through external emulator. For TMDSEVM6474LE, CCSv4 interfaces with the board only via XDS560v2 System Trace emulator using the USB cable supplied.

To start operating the board, follow instructions in the Quick Setup Guide. Follow the instruction in <u>BIOS MCSDK</u> <u>Getting Started Guide</u> to install all the necessary development tools, drivers and documentation.

After the installation is completed, follow below steps to run Code Composer Studio.

- 1. Power ON the board using power brick adaptor (12V/2.5A) supplied along with this EVM or Insert this EVM board into MicroTCA chassis or AMC carrier back-plane.

- 2. Connect USB cable from host PC to EVM board for TMDSEVM6474L or to XDS560v2 Mezzanine emulator for TMDSEVM6474LE.

- 3. Launch Code Composer Studio from host PC by double clicking on its icon at PC desktop.

Detailed information about the EVM including examples and reference material is available in the DVD available with this EVM kit.

Page 13 / 48

### Technical Reference Manual

SPRUGX2 - Revised March 2011

Figure 1.4: TMDSEVM6474LE

### 1.4 Power Supply

The C6474 Lite EVM can be powered from a single +12V / 2.5A DC (30W) external power supply connected to the DC power jack (J8). Internally, +12V input is converted into desired voltage levels such as, +5V, +3.3V, +2.5V, +1.8V, +1.5V, +1.1V and CVDD (0.9V ~ 1.2V) using local DC-DC converters.

- CVDD is used for DSP Core (Smart Reflex support)

- +1.5V is used for FPGA core

- +1.8V is used for DSP GPIOs, DDR2 / FPGA IO, NAND flash interface

- +2.5V is used for Ethernet Switch

- +3.3V is used for Oscillators, MSP430, Test Header

- The DC power jack connector is a 2.5mm barrel-type plug with center-tip as positive polarity.

The C6474 Lite EVM can also draw power from the AMC edge connector (J1). If the board is inserted into a PICMG® MicroTCA.0 R1.0 compliant system chassis or AMC Carrier back-plane, an external +12V supply from DC jack (J8) is not required.

### 2. Introduction to the C6474 Lite EVM board

This chapter provides an introduction and details of interfaces for the C6474 Lite EVM board. It contains:

- 2.1 Memory Map

- 2.2 EVM Boot mode and Boot configuration switch settings

- 2.3 Clock Configuration

- 2.4 Board Revision ID

- 2.5 JTAG Emulation Overview

- 2.6 Clock Domains

- 2.7 I2C boot EEPROM

- 2.8 FPGA

- 2.9 Ethernet Switch

- 2.10 Serial RapidIO(SRIO) Interfaces

- 2.11 Antenna Interface (AIF)

- 2.12 UART Interfaces

- 2.13 Module Management Controller for IPMI

- 2.14 Additional Headers

### 2.1 Memory Map

The memory map of the TMS320C6474 device is as shown in Table 1. It provides a combined view of both local and global addresses. The C64x+ Megamodule local memories have both local and global addresses. The Megamodule registers have only local addresses which can be resolved within the Megamodule and cannot be accessed outside Megamodule. All other addresses listed in this table are global addresses which can be accessed from any bus master including all three C64x+ Megamodules, transfer controllers within the EDMA block and any peripheral that can master the bus.

| Six Address Range      | Memory Block Description               |  |

|------------------------|----------------------------------------|--|

| 0x 00000000 - 007FFFFF | Reserved                               |  |

| 0x 00800000 – 008FFFFF | L2 SRAM                                |  |

| 0x 00900000 – 00FFFFFF | L1P and L1D SRAM, Reserved             |  |

| 0x 01000000 - 01BFFFFF | C64x+ Megamodule Registers             |  |

| 0x 01C00000 - 027FFFFF | Reserved                               |  |

| 0x 02800000 - 0FFFFFF  | Control Registers on CFG SCR, Reserved |  |

| 0x 10000000 - 1FFFFFF  | Global RAM, Reserved                   |  |

| 0x 20000000 - 6FFFFFF  | Data space on EDMA SCR, Reserved       |  |

| 0x 70000000 - 7FFFFFF  | DDR2 EMIF Config, Reserved             |  |

| 0x 80000000 - 9FFFFFF  | DDR2 EMIF Data                         |  |

| 0x A0000000 - AFFFFFF  | AIF Data                               |  |

| 0x B0000000 - FFFFFFFF | Reserved                               |  |

#### Table 1: TMS320C6474 Memory Map

### 2.2 EVM Boot mode and Boot configuration switch settings

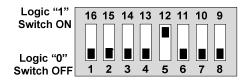

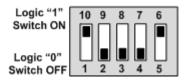

The C6474 Lite EVM has 13 sliding DIP switches (Board Ref. SW3 and SW4) to determine boot mode, device number, Endian mode and DSP Core clock select (System/Alternate) options at every reset of the DSP.

The EVM contains DSP configuration options that are both user-defined and fixed which need to be known during DSP software development. The fixed configuration options are set up for proper EVM operation while user-defined parameters can be set by using configuration switches SW3 and SW4; SW3 determines device number and core clock source for DSP while SW4 determines DSP boot mode and little or big endian mode.

Whenever the user presses a Cold or Warm Reset button or power-cycles the board, an on-board FPGA latches the state of configuration inputs switches and presents them to DSP during reset period.

The configuration inputs which are multiplexed with GPIO pins are driven out from the FPGA only when RESETSTAT is low. This allows these configuration inputs to be latched by DSP when reset is released. Thereafter, they can be used in the GPIO mode to perform communication with FPGA.

For more information on the boot mode, refer <u>TMS320C6474 Datasheet</u> and TMS320C6474 Bootloader User's Guide (<u>TMS320C645x/C647x DSP Bootloader User's Guide</u>).

SW4 defines the DSP boot mode and DEVNUM pins for the EVM. There are 5 positions, which are described below:

- SW4 positions 4, 3, 2 and 1  $\rightarrow$  Boot Mode Selection (BOOTMODE [3:0])

- SW4 position 5 → Device Endian mode (LENDIAN)

SW3 defines DEVNUM pins and core clock select. There are 8 positions, which are described below:

- SW3 positions 4, 3, 2 and 1  $\rightarrow$  Device Number (DEVNUM[3:0])

- SW3 position 5  $\rightarrow$  Core clock select (CORECLKSEL)

- SW3 position 8, 7, 6  $\rightarrow$  User Switches

Please refer section 4.3.3 of this document for default switch setting and details of each switch.

### 2.3 Clock Configuration

Table 3 shows clock configuration information of the EVM.

| Table 2: Cloc | <b>c</b> Configurations |

|---------------|-------------------------|

|---------------|-------------------------|

| Clock         | Frequency | Description                                         |

|---------------|-----------|-----------------------------------------------------|

| ALTCORECLKN/P | 50.000MHz | Clock Input for PLL1 (Differential)                 |

| DDRREFCLKN/P  | 66.000MHz | DDR Reference Clock Input to DDR PLL (Differential) |

### 2.4 Board Revision ID

Board PCB (Printed Circuit Board) and PCA (Printed Circuit Assembly) revision are located below RJ-45 Jack in bottom silk, as shown below.

Figure 2.1: EVM Board Revision

Table 3 indicates the interpretation of PCA/PCB revisions; last two digits represent major PCB / PCA revision number.

| PCA REV     | PCB REV     | Description                                |

|-------------|-------------|--------------------------------------------|

| 18-00080-01 | 17-00080-01 | Proto boards (Initial engineering samples) |

| 18-00080-02 | 17-00080-02 | Production boards                          |

### 2.5 JTAG - Emulation Overview

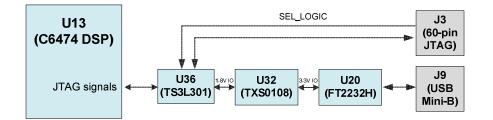

#### 2.5.1 JTAG – TMDSEVM6474L

The EVM supports two different types of DSP Emulation - "USB mini-B" and "60-pin TI JTAG-DSP".

USB emulation is supported through an on-board, optimized XDS100-class embedded emulation circuit. Onboard (embedded) USB emulation is accessible through the USB mini-B connector (J9); hence any external emulator is not necessary to connect EVM with Code Composer Studio. User can connect CCS with target DSP in EVM with USB cable supplied along with this board.

TI 60-pin JTAG header (J3) is provided on-board to allow user to connect to external emulator for high speed real-time emulation. External/mezzanine emulators as XDS560v2 emulators and standard XDS510 or XDS560 emulators with 60 to 20-pin or 60 to 14-pin adapter boards from TI and 3rd-party vendors are supported. Please refer to the documentation supplied with your emulator for connection assistance.

Both emulator configurations are enabled by default and there is dynamic switching between them. On-board embedded JTAG emulator is default connection to DSP, however when external emulator is connected to EVM, board circuitry automatically switches to give access to external emulator. When both are connected at the same time, external emulator is given priority and on-board emulator is disconnected from DSP.

The interface between DSP, on-board and external emulator is shown in figure below:

Figure 2.2: TMDSEVM6474L JTAG emulation

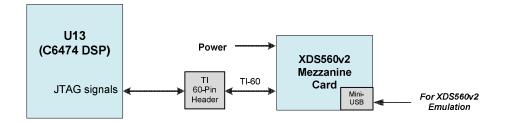

#### 2.5.2 JTAG – TMDSEVM6474LE

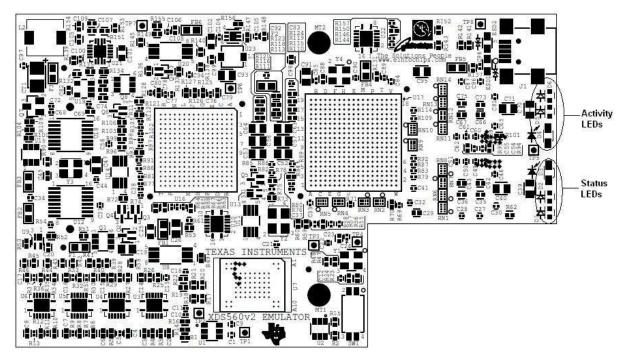

In TMDSEVM6474LE, high speed real time emulation can be performed without needing an external emulator as it has an integrated, system trace capable XDS560v2 Mezzanine Emulator mounted on its TI 60-pin JTAG header (J3). User can connect the EVM to CCS by connecting the USB port of XDS560 Mezzanine emulator to PC using USB cable supplied with an EVM.

As high speed XDS560v2 Emulator is already mounted on TI 60-pin JTAG header of the EVM, the low speed XDS100 emulation is no longer required and not available to user.

It is important to note that for XDS560v2 emulation, the USB cable needs to be connected to the mini-AB connector (J1) on XDS560v2 Mezzanine emulator and not to mini-B connector (J9) on the main board. For TMDSEVM6474LE, the mini-B connector (J9) on the main board can be used to access UART-over-USB; please refer to section 2.12 of this document for more details.

The interface between DSP and XDS560v2 Mezzanine Emulator is shown in figure 2.3:

Figure 2.3: TMDSEVM6474LE JTAG emulation

#### 2.5.2.1 XDS560v2 Mezzanine Emulator Booting

When TMDSEVM6474LE is powered ON, the XDS560v2 mezzanine emulator starts booting. It takes approximately half minute to boot-up. The successful booting of XDS560v2 mezzanine emulator is indicated by following LEDs sequence:

- Green LED (D3) turns ON

- Yellow LED (D2) and Red LED (D1) turns ON

- Green LED (D3) blinks and turns OFF

After the completion of booting XDS560v2 mezzanine emulator is ready to interface with CCS. Once CCS is connected to the target DSP Green LED D4 turns ON.

The boot failure is indicated by simultaneous blinking of Red LED (D1), Yellow LED (D2) and Green LED (D3). In this case CCS can't be connected to XDS560v2 mezzanine emulator. The boot failure can happen when mezzanine emulator is attempted to mount over a non-compatible base EVM.

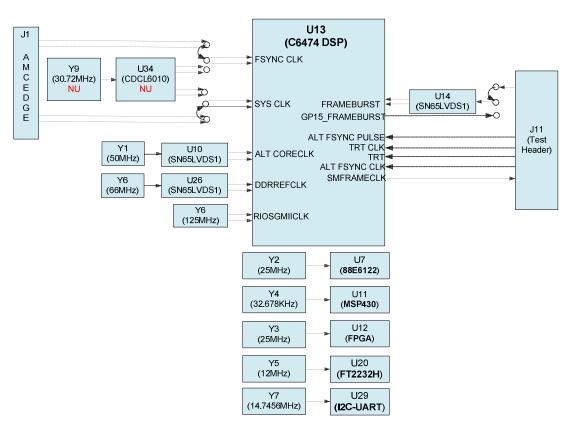

### 2.6 Clock Domains

The EVM incorporates variety of clocks to the TMS320C6474 as well as other devices which are configured automatically during the power up configuration sequence. The figure below illustrates the clocking for the system in EVM module. Please note that Y9 and U34 are not normally installed on the EVM.

#### Figure 2.4: C6474 Lite EVM Clock Domains

### 2.7 I2C Boot EEPROM

The I2C EEPROM address 0x50 contains Power on Self Test (POST) program and I2C address 0x51 contains second level boot-loader program. The second level boot-loader reads the Out-Of-Box Demo program from the NAND FLASH memory.

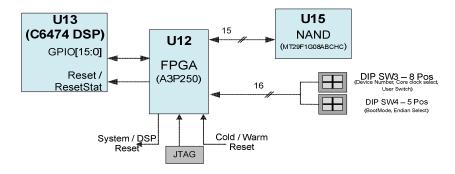

### 2.8 FPGA

The FPGA (Actel #A3P250-FGG144) interface provides reset control circuitry and latching of device configuration pins. The logic level of these pins is latched at reset to determine the device configuration. These switch-controlled inputs are driven to the DSP at reset time.

FPGA supports two modes; Normal mode and NAND pass through mode. These modes are mutually exclusive modes. In Normal mode, FPGA provides access to FPGA registers through DSP's GPIO pins. FPGA supports 2 user LEDs and 3 User Switches through control registers.

In NAND pass through mode, DSP GPIOs are directly assigned to NAND pins. NAND access is only possible in NAND pass through mode. Details of these are provided in chapter 3 <u>FPGA Functional Specification</u>.

Below figure shows interface between C6474 DSP and FPGA.

Figure 2.5: C6474 Lite EVM FPGA Connections

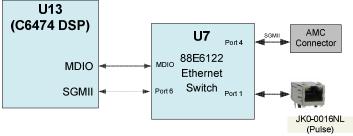

### 2.9 Ethernet Switch

The C6474 Lite EVM incorporates an Ethernet Switch 88E6122 with 2 Gigabit PHYs. Ethernet Switch's Port 6 is configured for SGMII interface with DSP, Port 1 is configured for copper interface to interface with external world through RJ-45 connector and port 4 is taken to the AMC connector in SGMII mode. RJ45 connector (J2) and Port 0 of AMC edge connector allows Gigabit Ethernet access to the SGMII port of C6474 DSP. At Power On, the Ethernet switch will be configured by the configuration EEPROM (U22). The default configuration will ensure the connectivity of DSP SGMII port to RJ45 connector and Port 0 of AMC edge connector.

Interface between DSP (U13) and Switch (U7) is shown in figure below.

Figure 2.6: C6474 Lite EVM Ethernet Switch Routing

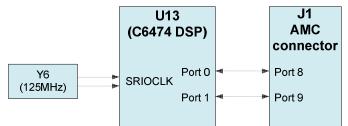

### 2.10 Serial RapidIO (SRIO) Interface

The C6474 Lite EVM supports high speed SERDES based Serial RapidIO (SRIO) interface. There are total two 1x RapidIO ports available on C6474. All SRIO ports are routed to AMC edge connector on board as per the PICMG AMC.0 R2.0 specifications. The SRIO ports 1-2 are routed to AMC ports 8-9 respectively. Below figure shows RapidIO connections between the DSP and AMC edge connector.

Figure 2.7: C6474 Lite EVM SRIO Port Connections

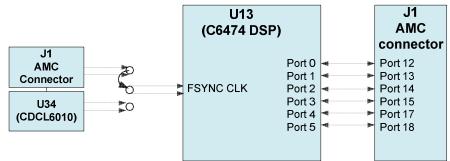

### 2.11 Antenna Interfaces

The C6474 Lite EVM has a high speed SERDES based Antenna Interface (AIF). There are total 6 AIF ports available on C6474. All AIF ports are taken to AMC edge connector on board. The figure below shows the AIF connections between DSP and AMC connector.

Figure 2.8: C6474 Lite EVM AIF Port Connections

### 2.12 UART Interface

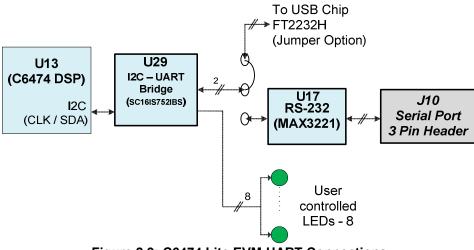

A serial port is provided for debugging purpose using an I2C-UART bridge. This serial port can be accessed either through USB connector (J9) or through 3-pin serial port header (J10). The selection can be made through UART Route Select shunt J13 as follows:

- UART over mini-USB Connector (J9) Shunts installed over J13.3-J13.1 and J13.4 -J13.2 (Default)

- UART over 3-Pin Header J10 Shunts installed over J13.3-J13.5 and J13.4 -J13.6

A 3-pin to 9-pin DTE (Data Terminal Equipment) serial cable is provided in the EVM kit to connect the J10 serial port to PC. An additional UART port is also routed from I2C-UART Bridge to 80 pin header J11.

Figure 2.9: C6474 Lite EVM UART Connections

### 2.13 Module Management Controller (MMC) for IPMI

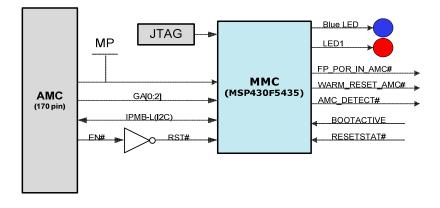

The C6474 Lite EVM supports limited set of Intelligent Platform Management Interface (IPMI) commands using Module Management Controller (MMC) based on Texas Instruments MSP430F5435 mixed signal processor.

The MMC will communicate with MicroTCA Carrier Hub (MCH) over IPMB (Intelligent Platform Management Bus) when inserted into AMC slot of a PICMG® MTCA.0 R1.0 compliant chassis. The primary purpose of the MMC is to provide necessary information to MCH, to enable the payload power to the C6474 Lite EVM when it is inserted into the MicroTCA chassis.

The EVM also supports a Blue LED and LED1 on the front panel as specified in PICMG® AMC.0 R2.0 AdvancedMC base specification. Both of these LEDs will blink as part of initialization process when the MMC will receive management power.

Blue LED:

Blue LED will turn ON when MicroTCA chassis is powered ON and an EVM is inserted into it. The blue LED will turn OFF when payload power is enabled to the EVM by the MCH.

#### <u>LED1:</u>

Red colored LED1 will normally be OFF. It will turn ON to provide basic feedback about failures and out of service.

Figure 2.10: C6474 Lite EVM MMC Connections for IPMI

#### 2.14 Additional Headers

The C6474 Lite EVM contains an 80 pin header (J11) which has GPIO, McBSP, Timer, FSYNC, I2C and UART signal connections. It shall be noted that I2C and UART connections to this header (J11) are of 3.3V level whereas GPIO, McBSP, Timer and FSYNC signals are of 1.8V level.

### 3. FPGA Functional Specification

This chapter contains an overview of the FPGA

- 3.1. FPGA modes

- 3.2. FPGA – DSP communication signals

- 3.3. FPGA memory map

- FPGA configuration registers 3.4.

- FPGA-DSP communication protocol in FPGA Normal mode 3.5.

- Sequence of Operation 3.6.

#### 3.1 **FPGA** modes

The FPGA can be configured in two modes. They are:

- 1. Normal mode

- 2. NAND pass through mode

After the completion of booting, DSP GPIO 14 is used to select between the Normal mode and the NAND Pass through mode.

If DSP GPIO 14 is 1'b0, then normal mode is selected. FPGA registers can be accessed in normal mode of operation only.

If DSP GPIO 14 is 1'b1, then Pass-Through mode is selected. In this mode DSP GPIO pins are directly mapped to the pins of the NAND Flash memory except Write-Protect Pin. The Write-Protect pin is not mapped due to unavailability of a GPIO pin in NAND pass through mode. The Write-Protect Pin of NAND Flash is mapped to the bit [4] of NAND CWR REGH FPGA register. The user application will require to disable write protect using the FPGA normal mode and then switch to NAND pass through mode to write to the NAND flash.

### **3.2 FPGA – DSP communication signals**

The GPIO signals used for communication between FPGA and DSP when FPGA is in Normal mode are described in Table 2. The GP [12:13] are not used.

| GPIO#   | Function               | Direction     | Description                                                                                                                                                                                                                                                                                                                             |  |  |  |

|---------|------------------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| GP[7:0] | Data                   | Bidirectional | This is 8-bit wide bidirectional bus, shared for address and data.<br>Whether the signals currently carry address, read data, or write data<br>is defined by the Command signals.                                                                                                                                                       |  |  |  |

| GP[9:8] | Command                | Input         | These bits define the bus operation for the current strobe period.<br>00 - NOP<br>01 - address cycle<br>10 - read cycle<br>11 - write cycle                                                                                                                                                                                             |  |  |  |

| GP10    | Strobe                 | Input         | This signal is used to synchronize the bus activity between the DSP and FPGA. The DSP is always master of the bus timing.                                                                                                                                                                                                               |  |  |  |

| GP11    | Ready                  | Output        | A low value on this pins during a read or write cycle will cause the DSP to extend the cycle until the signal goes high. This signal is not monitored for address and NOP cycles                                                                                                                                                        |  |  |  |

| GP14    | FPGA<br>mode<br>select | Input         | This signal selects the mode of communication with the NAND Flash<br>Memory. If it is 1'b1, then pass-through mode is enabled whereby<br>the DSP GPIO pins are directly mapped to the pins of NAND Flash<br>Memory. If it is 1'b0, then Normal Mode of operation is selected in<br>which FPGA Configuration Registers will be accessed. |  |  |  |

| GP 15   | I2C-UART<br>interrupt  | Output        | This signal directly follows the Bridge Interrupt input to FPGA.                                                                                                                                                                                                                                                                        |  |  |  |

| Table 4  | <b>1</b> · | GPIO | nin | mai | nina  | in | Normal | mode |

|----------|------------|------|-----|-----|-------|----|--------|------|

| I able - | τ.         |      | pin | ma  | oping |    | Normai | moue |

The GPIO signals used for communication between FPGA and DSP when FPGA is used in NAND pass through mode are described in Table 3.

| GPIO#   | Function               | Direction     | Description                                                                                                                                                                                                                                                                                                                             |

|---------|------------------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GP[7:0] | Data                   | Bidirectional | This 8-bit data bus is mapped to the 8-bit data bus of NAND Flash Memory.                                                                                                                                                                                                                                                               |

| GP[9:8] |                        |               | GP[8] pin is mapped to the Command Latch Enable (CLE) pin of NAND Flash Memory.                                                                                                                                                                                                                                                         |

| GF[9.0] | Command                | Input         | GP[9] pin is mapped to the Address Latch Enable (ALE) pin of NAND Flash Memory.                                                                                                                                                                                                                                                         |

| GP10    | Write<br>enable        | Input         | This signal is mapped to the Write Enable (nWE) pin of the NAND Flash Memory.                                                                                                                                                                                                                                                           |

| GP11    | Ready                  | Output        | This signal is mapped to the Ready/Busy (RB) pin of the NAND Flash Memory.                                                                                                                                                                                                                                                              |

| GP12    | Read<br>enable         | Input         | This signal is mapped to the Read Enable (nRE) pin of the NAND Flash Memory.                                                                                                                                                                                                                                                            |

| GP13    | Chip<br>enable         | Input         | This signal is mapped to the Chip Enable (nCE) pin of the NAND Flash Memory.                                                                                                                                                                                                                                                            |

| GP14    | FPGA<br>mode<br>select | Input         | This signal selects the mode of communication with the NAND Flash<br>Memory. If it is 1'b1, then pass-through mode is enabled whereby the<br>DSP GPIO pins are directly mapped to the pins of NAND Flash<br>Memory. If it is 1'b0, then Normal Mode of operation is selected in<br>which FPGA Configuration Registers will be accessed. |

| GP 15   | I2C-UART<br>interrupt  | Output        | This signal directly follows the Bridge Interrupt input to FPGA.                                                                                                                                                                                                                                                                        |

#### Table 5: GPIO pin mapping in NAND pass through mode

### 3.3 **FPGA** memory map

Table 4 describes the memory map of FPGA when FPGA is configured in Normal mode of operation.

#### Table 6: FPGA Memory Map

| GPIO[7:0]   | Memory                     |

|-------------|----------------------------|

| 0x00 – 0x22 | Configuration Memory Space |

# 3.4 FPGA configuration registers

The following table enlists the FPGA configuration register and its description:

|                 |                | Read / Default  |       | Data | Description                                                                                                                                                     |  |

|-----------------|----------------|-----------------|-------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Name            | Address        | Write           | value | bits | Description                                                                                                                                                     |  |

| Reserved        | 0x00 -<br>0x05 | -               | -     | 7:0  | Reserved for future use.                                                                                                                                        |  |

| BITFILE_VER_REG | 0x06           | Read            | 0x01  | 7:0  | Shows the BITFILE version                                                                                                                                       |  |

| RTL_VER_REG     | 0x07           | Read            | 0x01  | 7:0  | Shows the RTL version                                                                                                                                           |  |

| -               | 0x08           | -               | 0x00  | 7:0  | Reserved for future use.                                                                                                                                        |  |

| CONTROL_REGH    | 0x09           | Read /<br>Write | 0x70  | 3:0  | Reserved for future use.                                                                                                                                        |  |

|                 |                |                 |       | 4    | Write Protect Bit<br>1 => Disable<br>0 => Enable<br>This bit is mapped to the Write-Protect pin of<br>NAND Flash Memory if the Pass-Through Mode<br>is enabled. |  |

|                 |                |                 |       | 5    | User LED 0 Data. The bit value that is written at this location is driven on the User LED 0, if the User LED is enabled via NAND_CWR_REGH[7].                   |  |

|                 |                |                 |       | 6    | User LED 1 Data. The bit value that is written at this location is driven on the User LED 1, if the User LED is enabled via NAND_CWR_REGH[7].                   |  |

|                 |                |                 |       | 7    | User LED's Enable/Disable<br>0 => FPGA drives 1'b1 on User LED's (Disable)<br>1 => Data present in NAND_CWR_REGH [6:5] is<br>driven on the User LED's (Enable). |  |

| Reserved        | 0x0A –<br>0x21 | -               | -     | 7:0  | Reserved for future use. (RFU)                                                                                                                                  |  |

| USER_SW_REG     | 0x22           | Read            | 0x00  | 0    | tievm_user_sw1_i                                                                                                                                                |  |

|                 |                |                 |       | 1    | tievm_user_sw2_i                                                                                                                                                |  |

|                 |                |                 |       | 3    | tievm_user_sw3_i                                                                                                                                                |  |

|                 |                |                 |       | 4:2  | Reserved for future use                                                                                                                                         |  |

|                 |                |                 |       | 7:5  | tievm_board_ver_i[2:0]                                                                                                                                          |  |

#### Table 7: FPGA configuration Registers set

#### FPGA-DSP communication protocol in FPGA Normal mode 3.5

At system reset FPGA becomes master and DSP becomes slave. The FPGA will provide the boot parameters to DSP. Once booting is done the FPGA will become slave and DSP will become master, at this point the below mentioned protocol is implemented.

The 16 bit bus from DSP GPIO to FPGA is divided in

- 8-bit bi-directional bus which is shared between data and address.

- 4-bit for control and handshaking signals.

- 2-bits are not used.

DSP to FPGA has strobe based asynchronous communication.

After the DSP reset and boot sequence, the GPIO pins will transition from their configuration role to their role in the GPIO Bus. The DSP is the master of the GPIO BUS. The DSP will initiate bus cycles, define how long they last and when they will complete. The FPGA can extend a read or write cycle if needed.

The normal write sequence is for the DSP to issue an address cycle followed by a write cycle. The normal read sequence is for the DSP to issue an address cycles followed by a read cycle. If a read or write cycle is not preceded by an address cycle, the address of the last cycle is used. This allows repeated reads or writes to a given register.

To initiate an address cycle the DSP will:

- 1. Set the value of cmd

- 2. Set the direction of data io as output from DSP

- Set the address value on data\_io

Set stb\_o active

- 5. Wait a minimum of 50 ns

- 6. Set stb o inactive

- 7. Wait a minimum of 50 ns before the next cycle starts

#### Procedure 3-1: Address cycle Initiation by DSP

To initiate a write cycle the DSP will:

- 1. Set the value of cmd

- 2. Set the direction of data\_io as output from DSP

- 3. Set the write data value on data io

- 4. Set stb o active

- 5. Wait a minimum of 50 ns

- 6. If rdy o is low wait until it is high

- 7. Set stb o inactive

- 8. Wait a minimum of 50 ns before the next cycle starts

#### Procedure 3-2: Write cycle Initiation by DSP

To initiate a read cycle the DSP will:

- 1. Set the value of cmd

- 2. Set the direction of data\_io as input to DSP

- 3. Set stb\_o active

- 4. Wait a minimum of 50 ns

- 5. If rdy\_o is low wait until it is high

- 6. read data\_io and store as the read cycle result

- 7. Set stb\_o inactive

- 8. Wait a minimum of 50 ns before the next cycle starts

#### Procedure 3-3: Read Cycle Initiation by DSP

The FPGA will only enable its data\_io drive when cmd == READ and stb\_o is active. The FPGA must ensure that its driver is off no later than 40 ns after stb\_o goes inactive.

The bus may idle after any of the above cycles; an explicit NOP cycle is not needed

### 3.6 Sequence of Operation

Following section provides details of FPGA sequence of operation.

#### 3.6.1 Boot sequence – Power-On (Cold) Reset

- 1. On system reset (power-on reset), available through the global FPGA system reset pin, assert POR# and XWRST# pin active low

- 2. Wait for the FPGA internal PLL to stabilize

- Once the PLL is locked, user defined configuration pins and fixed configuration pins are latched by FPGA and pin status are provided to C6474 device configuration pins. For device configuration settings please refer sections <u>4.3.3 DSP Configurations</u> and <u>4.3.4 DSP boot mode</u>.

- Wait for 50 μS. As the frequency of operation of the FPGA is 25MHz, the internal counters would count 2000 clock cycles

- 5. De-assert XWRST#. Keep POR# asserted.

- 6. Wait for 200 mS. As the frequency of operation of the FPGA is 25MHz, the internal counters would count 8000000 clock cycles. De-assert POR#.

- 7. Wait for RESETSTAT# signal from DSP to go from low to high. GPIO lines to GIC modules would be put in tri-state condition

- If boot modes are for EMAC boot (0'b0100, 0'b0101, 0'b0110) on boot mode DIP input switch, wait for 4 seconds. Assert XWRST# and wait for 50 μS. De-assert XWRST#.

- 9. Indicate GIC module that the boot mode is over

#### Procedure 3-1: Power on Reset

#### 3.6.2 Boot sequence – Warm Reset

- 1. On warm reset, available through the push button switches on-board, assert XWRST# pin active low

- Once the PLL is locked, user defined configuration pins and fixed configuration pins are latched by FPGA and pin status are provided to C6474 device configuration pins. For device configuration settings please refer sections <u>4.3.3 DSP Configurations</u> and <u>4.3.4 DSP boot mode</u>.

- 3. Wait for 50 µS. As the frequency of operation of the FPGA is 25MHz, the internal counters would count 2000 clock cycles

- 4. De-assert XWRST#

- 5. Wait for RESETSTAT# signal from DSP to go from low to high. GPIO lines to GIC modules would be put in tri-state condition

- 6. Indicate GIC module that the boot mode is over

Procedure 3-1: Warm Reset

### 4. EVM Board Physical Specifications

This chapter describes the physical layout of the C6474 Lite EVM board and its connectors, switches and test points. It contains:

- 1.1. Board Layout

- 1.2. Connector Index

- 1.3. Switches

- 1.4. Test Points

- 1.5. System LEDs

### 4.1 Board Layout

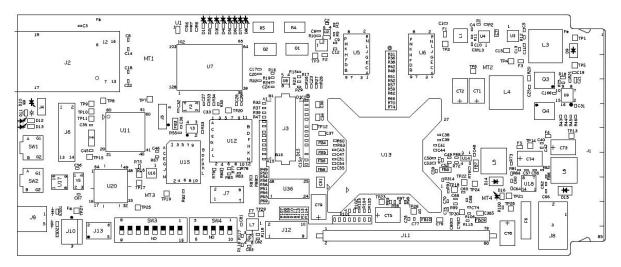

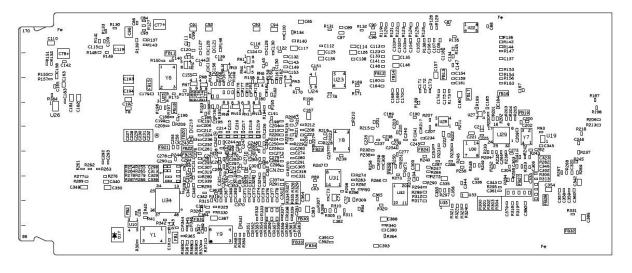

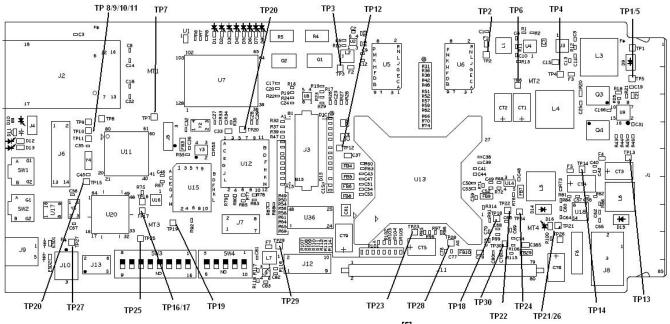

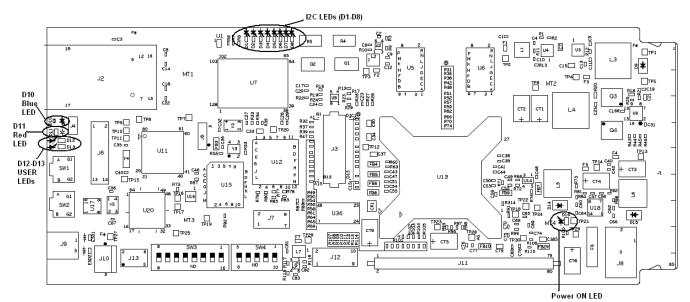

The C6474 Lite EVM board dimension is 7.11" x 2.89" (180.6mm x 73.5mm). It is a 12 layer board and powered through connector J8. Figure 3-1 and 3-2 shows assembly layout of the C6474 Lite EVM Board.

Figure 4.1: C6474 Lite EVM Board Assembly Layout - TOP view

### Technical Reference Manual

Figure 4.2: C6474 Lite EVM Board layout – Bottom view

#### 4.2 Connector Index

The C6474 Lite EVM Board has several connectors which provide access to various interfaces on the board.

| Connector | Pins | Function                                    |  |

|-----------|------|---------------------------------------------|--|

| J1        | 170  | AMC Edge Connector                          |  |

| J2        | 18   | Ethernet RJ-45 Connector                    |  |

| J3        | 60   | TI 60-Pin DSP JTAG Connector <sup>[3]</sup> |  |

| J4        | 2    | MSP Reset Jumper                            |  |

| J5        | 3    | Power selection for MSP430                  |  |

| J6        | 14   | MSP430 JTAG Connector                       |  |

| J8        | 3    | Power Input Jack Connector                  |  |

| J9        | 5    | Mini-B USB Connector                        |  |

| J10       | 3    | UART 3-Pin Connector                        |  |

| J11       | 80   | McBSP/GPIO/Timer Test Header                |  |

| J12       | 10   | FPGA JTAG Connector                         |  |

| J13       | 6    | UART Path Select Connector                  |  |

| J1 5      |      | Mini-AB USB Connector <sup>[4]</sup>        |  |

#### Table 8: TMS320C6474 Board Connectors

Note:

[3] – Not Available in TMDSEVM6474LE.

[4] – Present on XDS5602v2 Mezzanine Card. Available in TMDSEVM6474LE only.

#### 4.2.1 J1, AMC Edge Connector

The J1 card edge connector plugs into an AMC compatible carrier board and provides a high speed Serial RapidIO, AIF, SGMII and I2C interfaces to the carrier board. This connector is the 170-pin B+ style AMC connector. The signals on this connector are shown in the table below.

| Pin | Signal       | Description          | Pin | Signal         | Description     |

|-----|--------------|----------------------|-----|----------------|-----------------|

| 1   | GND          | Ground Signal        | 170 | GND            | Ground Signal   |

| 2   | VCC12        | +12V Power           | 169 | NC             |                 |

| 3   | PS1#         | Presence 1           | 168 | NC             |                 |

| 4   | MP           | Management Power     | 167 | NC             |                 |

| 5   | GA0          | Geographic Address 0 | 166 | NC             |                 |

| 6   | NC           |                      | 165 | NC             |                 |

| 7   | GND          | Ground Signal        | 164 | GND            | Ground Signal   |

| 8   | NC           |                      | 163 | NC             | <b>j</b>        |

| 9   | VCC12        | +12V Power           | 162 | NC             |                 |

| 10  | GND          | Ground Signal        | 161 | GND            | Ground Signal   |

| 11  | P4 SGMII TXP |                      | 160 | I2C_SDA        | I2C SDA         |

| 12  | P4 SGMII TXN |                      | 159 | I2C_SCL        | I2C SCL         |

| 13  | GND          | Ground Signal        | 158 | GND            | Ground Signal   |

| 14  | P4_SGMII_RXP | ~                    | 157 | ALT_FSYNC_CLKP | Alternate Frame |

| 15  | P4_SGMII_RXN |                      | 156 | ALT_FSYNC_CLKP | System clock    |

| 16  | GND          | Ground Signal        | 155 | GND            | Ground Signal   |

| 17  | GA1          | Geographic Address 1 | 154 | ALT_SYSCLKP    | Alternate       |

| 18  | VCC12        | +12V Power           | 153 | ALT_SYSCLKP    | System clock    |

| 19  | GND          | Ground Signal        | 152 | GND            | Ground Signal   |

| 20  | NC           |                      | 151 | AIF_TXP5       | AIF Port 5-TX   |

| 21  | NC           |                      | 150 | AIF_TXN5       | AIF Port 5-TX   |

| 22  | GND          | Ground Signal        | 149 | GND            | Ground Signal   |

| 23  | NC           |                      | 148 | AIF_RXP5       | AIF Port 5-RX   |

| 24  | NC           |                      | 147 | AIF_RXN5       | AIF Port 5-RX   |

| 25  | GND          | Ground Signal        | 146 | GND            | Ground Signal   |

| 26  | GA2          | Geographic Address 2 | 145 | AIF_TXP4       | AIF Port 4-TX   |

| 27  | VCC12        | +12V Power           | 144 | AIF_TXN4       | AIF Port 4-TX   |

| 28  | GND          | Ground Signal        | 143 | GND            | Ground Signal   |

| 29  | NC           |                      | 142 | AIF_RXP4       | AIF Port 4-RX   |

| 30  | NC           |                      | 141 | AIF_RXN4       | AIF Port 4-RX   |

| 31  | GND          | Ground Signal        | 140 | GND            | Ground Signal   |

| 32  | NC           |                      | 139 | NC             |                 |

| 33  | NC           |                      | 138 | NC             |                 |

| 34  | GND          | Ground Signal        | 137 | GND            | Ground Signal   |

| 35  | NC           |                      | 136 | NC             |                 |

| 36  | NC           |                      | 135 | NC             |                 |

| 37  | GND          | Ground Signal        | 134 | GND            | Ground Signal   |

| 38  | NC           |                      | 133 | AIF_TXP3       | AIF Port 3-TX   |

| 39  | NC           |                      | 132 | AIF_TXN3       | AIF Port 3-TX   |

| 40  | GND          | Ground Signal        | 131 | GND            | Ground Signal   |

| 41  | ENABLE#      | Enable Signal        | 130 | AIF_RXP3       | AIF Port 3-RX   |

| 42  | VCC12        | +12V Power           | 129 | AIF_RXN3       | AIF Port 3-RX   |

The Solutions People

### **Technical Reference Manual**

SPRUGX2 - Revised March 2011

### TMDSEVM6474L TMDSEVM6474LE

| 43 | GND      | Ground Signal | 128 | GND      | Ground Signal  |

|----|----------|---------------|-----|----------|----------------|

| 44 | NC       |               | 127 | AIF TXP2 | AIF Port 2-TX  |

| 45 | NC       |               | 126 | AIF TXN2 | AIF Port 2-TX  |

| 46 | GND      | Ground Signal | 125 | GND      | Ground Signal  |

| 47 | NC       |               | 124 | AIF RXP2 | AIF Port 2-RX  |

| 48 | NC       |               | 123 | AIF RXN2 | AIF Port 2-RX  |

| 49 | GND      | Ground Signal | 122 | GND      | Ground Signal  |

| 50 | NC       |               | 121 | AIF_TXP1 | AIF Port 1-TX  |

| 51 | NC       |               | 120 | AIF TXN1 | AIF Port 1-TX  |

| 52 | GND      | Ground Signal | 119 | GND      | Ground Signal  |

| 53 | NC       |               | 118 | AIF RXP1 | AIF Port 1-RX  |

| 54 | NC       |               | 117 | AIF RXN1 | AIF Port 1-RX  |

| 55 | GND      | Ground Signal | 116 | GND      | Ground Signal  |

| 56 | SCL IPMB |               | 115 | AIF TXP0 | AIF Port 0-TX  |

| 57 | VCC12    | +12V Power    | 114 | AIF TXN0 | AIF Port 0-TX  |

| 58 | GND      | Ground Signal | 113 | GND      | Ground Signal  |

| 59 | NC       |               | 112 | AIF RXP0 | AIF Port 0-RX  |

| 60 | NC       |               | 111 | AIF RXN0 | AIF Port 0-RX  |

| 61 | GND      | Ground Signal | 110 | GND      | Ground Signal  |

| 62 | NC       |               | 109 | NC       |                |

| 63 | NC       |               | 108 | NC       |                |

| 64 | GND      | Ground Signal | 107 | GND      | Ground Signal  |

| 65 | NC       |               | 106 | NC       |                |

| 66 | NC       |               | 105 | NC       |                |

| 67 | GND      | Ground Signal | 104 | GND      | Ground Signal  |

| 68 | NC       |               | 103 | NC       |                |

| 69 | NC       |               | 102 | NC       |                |

| 70 | GND      | Ground Signal | 101 | GND      | Ground Signal  |

| 71 | SDA_IPMB |               | 100 | NC       |                |

| 72 | VCC12    | +12V Power    | 99  | NC       |                |

| 73 | GND      | Ground Signal | 98  | GND      | Ground Signal  |

| 74 | NC       |               | 97  | RIO_TXP1 | SRIO Port 1-TX |

| 75 | NC       |               | 96  | RIO_TXN1 | SRIO Port 1-TX |

| 76 | GND      | Ground Signal | 95  | GND      | Ground Signal  |

| 77 | NC       |               | 94  | RIO_RXP1 | SRIO Port 1-RX |

| 78 | NC       |               | 93  | RIO_RXN1 | SRIO Port 1-RX |

| 79 | GND      | Ground Signal | 92  | GND      | Ground Signal  |

| 80 | NC       |               | 91  | RIO_TXP0 | SRIO Port 0-TX |

| 81 | NC       |               | 90  | RIO_TXN0 | SRIO Port 0-TX |

| 82 | GND      | Ground Signal | 89  | GND      | Ground Signal  |

| 83 | PS0#     | Presence 0    | 88  | RIO_RXP0 | SRIO Port 0-RX |

| 84 | VCC12    | +12V Power    | 87  | RIO_RXN0 | SRIO Port 0-RX |

| 85 | GND      | Ground Signal | 86  | GND      | Ground Signal  |

#### 4.2.2 J2, Ethernet Connector

J2 is Gigabit RJ45 Ethernet connector with integrated magnetic. It is driven from the 88E6122 Marvell Switch device. The connections are shown in the table below.

| Pin # | Signal Name  |

|-------|--------------|

| 1     | Center Tap 2 |

| 2     | MD2-         |

| 3     | MD2+         |

| 4     | MD1-         |

| 5     | MD1+         |

| 6     | Center Tap 1 |

| 7     | Center Tap 3 |

| 8     | MD3+         |

| 9     | MD3-         |

| 10    | MD0-         |

| 11    | MD0+         |

| 12    | Center Tap 0 |

| 13    | LED1-        |

| 14    | LED1+        |

| 15    | LED2-        |

| 16    | LED2+        |

| 17    | Shield 1     |

| 18    | Shield 2     |

#### Table 10: Ethernet Connector pin out

# 4.2.3 J3, DSP JTAG Connector

J3 is a standard TI 60 pin JTAG connector for XDS560v2 Emulator. The onboard switch multiplexes this interface with the onboard emulation interface. When an external emulator is plugged into J5, the external emulator can connect with the DSP. The I/O voltage level on these pins is 1.8V. So any 1.8V compatible emulator can be used to interface to the C6474 device. Note, that when an external emulator is plugged into this connector (J3), the onboard emulation circuitry will be disabled. The pin out for the connector is shown in the table below.

| Pin #Signal NamePin #Signal NameB1ID0D1NCA1GroundC1ID2B2TMSD2GroundA2GroundC2EMU18B3EMU17D3GroundA3GroundC3TRSTB4TDID4GroundA4GroundC4EMU16B5EMU14D5GroundA5GroundC5EMU15B6EMU12D6GroundA6GroundC6EMU13B7TDOD7GroundA7GroundC7EMU11B8TVDD8Type1 (Ground)A8Type0 (NC)C8TCLKRTNB9EMU9D9GroundA10GroundC10EMU8B11EMU5D11GroundA11GroundC11EMU6B12TCLKD12GroundA13GroundC13EMU3B14EMU0D14GroundA14GroundC14EMU1B15ID1D15GroundA15TRGRSTzC15ID3 |     |            |     |                |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------------|-----|----------------|--|--|

| A1GroundC1ID2B2TMSD2GroundA2GroundC2EMU18B3EMU17D3GroundA3GroundC3TRSTB4TDID4GroundA4GroundC4EMU16B5EMU14D5GroundA5GroundC5EMU15B6EMU12D6GroundA6GroundC6EMU13B7TDOD7GroundA7GroundC7EMU11B8TVDD8Type1 (Ground)A8Type0 (NC)C8TCLKRTNB9EMU9D9GroundA10GroundC10EMU8B11EMU5D11GroundA11GroundC11EMU6B12TCLKD12GroundA12GroundC12EMU4B13EMU2D13GroundA14GroundC14EMU3B14EMU0D14GroundA14GroundC14EMU1B15ID1D15Ground                          |     |            |     |                |  |  |

| B2TMSD2GroundA2GroundC2EMU18B3EMU17D3GroundA3GroundC3TRSTB4TDID4GroundA4GroundC4EMU16B5EMU14D5GroundA5GroundC5EMU15B6EMU12D6GroundA6GroundC6EMU13B7TDOD7GroundA7GroundC7EMU11B8TVDD8Type1 (Ground)A8Type0 (NC)C8TCLKRTNB9EMU9D9GroundA10GroundC10EMU8B11EMU5D11GroundA11GroundC11EMU6B12TCLKD12GroundA13EMU2D13GroundA13GroundC13EMU3B14EMU0D14GroundA14GroundC14EMU1B15ID1D15Ground                                                       |     |            |     |                |  |  |

| A2GroundC2EMU18B3EMU17D3GroundA3GroundC3TRSTB4TDID4GroundA4GroundC4EMU16B5EMU14D5GroundA5GroundC5EMU15B6EMU12D6GroundA6GroundC6EMU13B7TDOD7GroundA7GroundC7EMU11B8TVDD8Type1 (Ground)A8Type0 (NC)C8TCLKRTNB9EMU9D9GroundA9GroundC10EMU8B11EMU5D11GroundA12GroundC12EMU4B13EMU2D13GroundA13GroundC14EMU3B14EMU0D14Ground                                                                                                                    |     |            |     |                |  |  |

| B3EMU17D3GroundA3GroundC3TRSTB4TDID4GroundA4GroundC4EMU16B5EMU14D5GroundA5GroundC5EMU15B6EMU12D6GroundA6GroundC6EMU13B7TDOD7GroundA7GroundC7EMU11B8TVDD8Type1 (Ground)A8Type0 (NC)C8TCLKRTNB9EMU9D9GroundA9GroundC10EMU8B11EMU5D11GroundA11GroundC12EMU4B13EMU2D13GroundA12GroundC13EMU3B14EMU0D14GroundA14GroundC14EMU1B15ID1D15Ground                                                                                                    |     |            |     |                |  |  |

| A3GroundC3TRSTB4TDID4GroundA4GroundC4EMU16B5EMU14D5GroundA5GroundC5EMU15B6EMU12D6GroundA6GroundC6EMU13B7TDOD7GroundA7GroundC7EMU11B8TVDD8Type1 (Ground)A8Type0 (NC)C8TCLKRTNB9EMU9D9GroundA9GroundC10EMU8B11EMU5D11GroundA10GroundC12EMU6B12TCLKD12GroundA13GroundC13EMU3B14EMU0D14GroundA14GroundC14EMU1B15ID1D15Ground                                                                                                                   |     |            |     | EMU18          |  |  |

| B4TDID4GroundA4GroundC4EMU16B5EMU14D5GroundA5GroundC5EMU15B6EMU12D6GroundA6GroundC6EMU13B7TDOD7GroundA7GroundC7EMU11B8TVDD8Type1 (Ground)A8Type0 (NC)C8TCLKRTNB9EMU9D9GroundA9GroundC10EMU8B11EMU5D11GroundA11GroundC11EMU6B12TCLKD12GroundA13EMU2D13GroundA13GroundC13EMU3B14EMU0D14GroundA14GroundC14EMU1B15ID1D15Ground                                                                                                                 |     | EMU17      |     |                |  |  |

| A4GroundC4EMU16B5EMU14D5GroundA5GroundC5EMU15B6EMU12D6GroundA6GroundC6EMU13B7TDOD7GroundA7GroundC7EMU11B8TVDD8Type1 (Ground)A8Type0 (NC)C8TCLKRTNB9EMU9D9GroundA9GroundC10EMU8B10EMU7D10GroundA11GroundC11EMU8B12TCLKD12GroundA12GroundC13EMU4B13EMU2D13GroundA13GroundC14EMU3B14EMU0D14GroundA14GroundC14EMU1B15ID1D15Ground                                                                                                              |     | Ground     |     |                |  |  |

| B5EMU14D5GroundA5GroundC5EMU15B6EMU12D6GroundA6GroundC6EMU13B7TDOD7GroundA7GroundC7EMU11B8TVDD8Type1 (Ground)A8Type0 (NC)C8TCLKRTNB9EMU9D9GroundA9GroundC9EMU10B10EMU7D10GroundA11GroundC11EMU8B12TCLKD12GroundA12GroundC13EMU4B13EMU2D13GroundA13GroundC14EMU3B14EMU0D14GroundA14GroundC14EMU1B15ID1D15Ground                                                                                                                             |     | TDI        |     | Ground         |  |  |

| A5GroundC5EMU15B6EMU12D6GroundA6GroundC6EMU13B7TDOD7GroundA7GroundC7EMU11B8TVDD8Type1 (Ground)A8Type0 (NC)C8TCLKRTNB9EMU9D9GroundA9GroundC9EMU10B10EMU7D10GroundA10GroundC10EMU8B11EMU5D11GroundA11GroundC12EMU4B13EMU2D13GroundA13GroundC13EMU3B14EMU0D14GroundA14GroundC14EMU1B15ID1D15Ground                                                                                                                                            |     |            |     | EMU16          |  |  |

| B6EMU12D6GroundA6GroundC6EMU13B7TDOD7GroundA7GroundC7EMU11B8TVDD8Type1 (Ground)A8Type0 (NC)C8TCLKRTNB9EMU9D9GroundA9GroundC9EMU10B10EMU7D10GroundA10GroundC10EMU8B11EMU5D11GroundA11GroundC11EMU6B12TCLKD12GroundA13EMU2D13GroundA13GroundC13EMU3B14EMU0D14GroundA14GroundC14EMU1B15ID1D15Ground                                                                                                                                           | B5  | EMU14      |     | Ground         |  |  |

| A6GroundC6EMU13B7TDOD7GroundA7GroundC7EMU11B8TVDD8Type1 (Ground)A8Type0 (NC)C8TCLKRTNB9EMU9D9GroundA9GroundC9EMU10B10EMU7D10GroundA10GroundC10EMU8B11EMU5D11GroundA11GroundC11EMU6B12TCLKD12GroundA13EMU2D13GroundA13GroundC13EMU3B14EMU0D14GroundA14GroundC14EMU1B15ID1D15Ground                                                                                                                                                          |     |            |     | EMU15          |  |  |

| B7TDOD7GroundA7GroundC7EMU11B8TVDD8Type1 (Ground)A8Type0 (NC)C8TCLKRTNB9EMU9D9GroundA9GroundC9EMU10B10EMU7D10GroundA10GroundC10EMU8B11EMU5D11GroundA11GroundC11EMU6B12TCLKD12GroundA13EMU2D13GroundA13GroundC13EMU3B14EMU0D14GroundA14GroundC14EMU1B15ID1D15Ground                                                                                                                                                                         | B6  | EMU12      | D6  | Ground         |  |  |

| A7GroundC7EMU11B8TVDD8Type1 (Ground)A8Type0 (NC)C8TCLKRTNB9EMU9D9GroundA9GroundC9EMU10B10EMU7D10GroundA10GroundC10EMU8B11EMU5D11GroundA11GroundC11EMU6B12TCLKD12GroundA13EMU2D13GroundA13GroundC13EMU3B14EMU0D14GroundA14GroundC14EMU1B15ID1D15Ground                                                                                                                                                                                      | A6  | Ground     | C6  | EMU13          |  |  |

| B8TVDD8Type1 (Ground)A8Type0 (NC)C8TCLKRTNB9EMU9D9GroundA9GroundC9EMU10B10EMU7D10GroundA10GroundC10EMU8B11EMU5D11GroundA11GroundC11EMU6B12TCLKD12GroundA13EMU2D13GroundA13GroundC13EMU3B14EMU0D14GroundA14GroundC14EMU1B15ID1D15Ground                                                                                                                                                                                                     | B7  | TDO        |     | Ground         |  |  |

| A8Type0 (NC)C8TCLKRTNB9EMU9D9GroundA9GroundC9EMU10B10EMU7D10GroundA10GroundC10EMU8B11EMU5D11GroundA11GroundC11EMU6B12TCLKD12GroundA13EMU2D13GroundA13GroundC13EMU3B14EMU0D14GroundA14GroundC14EMU1B15ID1D15Ground                                                                                                                                                                                                                          | A7  | Ground     | C7  | EMU11          |  |  |

| B9EMU9D9GroundA9GroundC9EMU10B10EMU7D10GroundA10GroundC10EMU8B11EMU5D11GroundA11GroundC11EMU6B12TCLKD12GroundA12GroundC12EMU4B13EMU2D13GroundA13GroundC13EMU3B14EMU0D14GroundA14GroundC14EMU1B15ID1D15Ground                                                                                                                                                                                                                               | B8  |            |     | Type1 (Ground) |  |  |

| A9GroundC9EMU10B10EMU7D10GroundA10GroundC10EMU8B11EMU5D11GroundA11GroundC11EMU6B12TCLKD12GroundA12GroundC12EMU4B13EMU2D13GroundA13GroundC13EMU3B14EMU0D14GroundA15ID1D15Ground                                                                                                                                                                                                                                                             | A8  | Type0 (NC) | C8  | TCLKRTN        |  |  |

| B10EMU7D10GroundA10GroundC10EMU8B11EMU5D11GroundA11GroundC11EMU6B12TCLKD12GroundA12GroundC12EMU4B13EMU2D13GroundA13GroundC13EMU3B14EMU0D14GroundA15ID1D15Ground                                                                                                                                                                                                                                                                            | B9  | EMU9       | D9  | Ground         |  |  |

| A10GroundC10EMU8B11EMU5D11GroundA11GroundC11EMU6B12TCLKD12GroundA12GroundC12EMU4B13EMU2D13GroundA13GroundC13EMU3B14EMU0D14GroundA14GroundC14EMU1B15ID1D15Ground                                                                                                                                                                                                                                                                            | A9  | Ground     | C9  | EMU10          |  |  |

| B11EMU5D11GroundA11GroundC11EMU6B12TCLKD12GroundA12GroundC12EMU4B13EMU2D13GroundA13GroundC13EMU3B14EMU0D14GroundA14GroundC14EMU1B15ID1D15Ground                                                                                                                                                                                                                                                                                            | B10 | EMU7       | D10 | Ground         |  |  |

| A11GroundC11EMU6B12TCLKD12GroundA12GroundC12EMU4B13EMU2D13GroundA13GroundC13EMU3B14EMU0D14GroundA14GroundC14EMU1B15ID1D15Ground                                                                                                                                                                                                                                                                                                            | A10 | Ground     | C10 | EMU8           |  |  |

| B12TCLKD12GroundA12GroundC12EMU4B13EMU2D13GroundA13GroundC13EMU3B14EMU0D14GroundA14GroundC14EMU1B15ID1D15Ground                                                                                                                                                                                                                                                                                                                            | B11 | EMU5       | D11 | Ground         |  |  |

| A12GroundC12EMU4B13EMU2D13GroundA13GroundC13EMU3B14EMU0D14GroundA14GroundC14EMU1B15ID1D15Ground                                                                                                                                                                                                                                                                                                                                            | A11 | Ground     | C11 | EMU6           |  |  |