# TCIEVMK2LX Technical Reference Manual Version 1.0

Revised December 2014

# **Document Copyright**

## **Publication Title:**

Keystone2 EVM Technical Reference Manual All Rights Reserved. Reproduction, adaptation, or translation without prior written permission is prohibited, except as allowed under the copyright laws.

# ADDITIONAL TERMS AND CONDITIONS, WARNINGS, RESTRICTIONS, AND DISCLAIMERS FOR EVALUATION MODULES

Texas Instruments Incorporated (TI) markets, sells, and loans all evaluation boards, kits, and/or modules (EVMs) pursuant to, and user expressly acknowledges, represents, and agrees, and takes sole responsibility and risk with respect to, the following:

- 1. User agrees and acknowledges that EVMs are intended to be handled and used for feasibility evaluation only in laboratory and/or development environments. Notwithstanding the foregoing, in certain instances, TI makes certain EVMs available to users that do not handle and use EVMs solely for feasibility evaluation only in laboratory and/or development environments, but may use EVMs in a hobbyist environment. All EVMs made available to hobbyist users are FCC certified, as applicable. Hobbyist users acknowledge, agree, and shall comply with all applicable terms, conditions, warnings, and restrictions in this document and are subject to the disclaimer and indemnity provisions included in this document.

- 2. Unless otherwise indicated, EVMs are not finished products and not intended for consumer use. EVMs are intended solely for use by technically qualified electronics experts who are familiar with the dangers and application risks associated with handling electrical mechanical components, systems, and subsystems.

- 3. User agrees that EVMs shall not be used as, or incorporated into, all or any part of a finished product.

- 4. User agrees and acknowledges that certain EVMs may not be designed or manufactured by TI.

- 5. User must read the user's guide and all other documentation accompanying EVMs, including without limitation any warning or restriction notices, prior to handling and/or using EVMs. Such notices contain important safety information related to, for example, temperatures and voltages. For additional information on TI's environmental and/or safety programs, please visit <a href="www.ti.com/esh">www.ti.com/esh</a> or contact TI.

- 6. User assumes all responsibility, obligation, and any corresponding liability for proper and safe handling and use of EVMs.

- 7. Should any EVM not meet the specifications indicated in the user's guide or other documentation accompanying such EVM, the EVM may be returned to TI within 30 days from the date of delivery for a full refund. THE FOREGOING LIMITED WARRANTY IS THE EXCLUSIVE WARRANTY MADE BY TI TO USER AND IS IN LIEU OF ALL OTHER WARRANTIES, EXPRESSED, IMPLIED, OR STATUTORY, INCLUDING ANY WARRANTY OF MERCHANTABILITY OR FITNESS FOR ANY PARTICULAR PURPOSE. TI SHALL NOT BE LIABLE TO USER FOR ANY INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES RELATED TO THE HANDLING OR USE OF ANY EVM.

- 8. No license is granted under any patent right or other intellectual property right of TI covering or relating to any machine, process, or combination in which EVMs might be or are used. TI currently deals with a variety of customers, and therefore TI's arrangement with the user is not exclusive. TI assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services with respect to the handling or use of EVMs.

- 9. User assumes sole responsibility to determine whether EVMs may be subject to any applicable federal, state, or local laws and regulatory requirements (including but not limited to U.S. Food and Drug Administration regulations, if applicable) related to its handling and use of EVMs and, if applicable, compliance in all respects with such laws and regulations.

- 10. User has sole responsibility to ensure the safety of any activities to be conducted by it and its employees, affiliates, contractors or designees, with respect to handling and using EVMs. Further, user is responsible to ensure that any interfaces (electronic and/or mechanical) between EVMs and any human body are designed with suitable isolation and means to safely limit accessible leakage currents to minimize the risk of electrical shock hazard.

- 11. User shall employ reasonable safeguards to ensure that user's use of EVMs will not result in any property damage, injury or death, even if EVMs should fail to perform as described or expected.

- 12. User shall be solely responsible for proper disposal and recycling of EVMs consistent with all applicable federal, state, and local requirements.

Certain Instructions. User shall operate EVMs within TI's recommended specifications and environmental considerations per the user's guide, accompanying documentation, and any other applicable requirements. Exceeding the specified ratings (including but not limited to input and output voltage, current, power, and environmental ranges) for EVMs may cause property damage, personal injury or death. If there are questions concerning these ratings, user should contact a TI field representative prior to connecting interface electronics including input power and intended loads. Any loads applied outside of the specified output range may result in unintended and/or inaccurate operation and/or possible permanent damage to the EVM and/or interface electronics. Please consult the applicable EVM user's guide prior to connecting any load to the EVM output. If there is uncertainty as to the load specification, please contact a TI field representative. During normal operation, some circuit components may have case temperatures greater than 60°C as long as the input and output are maintained at a normal ambient operating temperature. These components include but are not limited to linear regulators, switching transistors, pass transistors, and current sense resistors which can be identified using EVMs' schematics located in the applicable EVM user's guide. When placing measurement probes near EVMs during normal operation, please be aware that EVMs may become very warm. As with all electronic evaluation tools, only qualified personnel knowledgeable in electronic measurement and diagnostics normally found in development environments should use EVMs.

Agreement to Defend, Indemnify and Hold Harmless. User agrees to defend, indemnify, and hold TI, its directors, officers, employees, agents, representatives, affiliates, licensors and their representatives harmless from and against any and all claims, damages, losses, expenses, costs and liabilities (collectively, "Claims") arising out of, or in connection with, any handling and/or use of EVMs. User's indemnity shall apply whether Claims arise under law of tort or contract or any other legal theory, and even if EVMs fail to perform as described or expected.

Safety-Critical or Life-Critical Applications. If user intends to use EVMs in evaluations of safety critical applications (such as life support), and a failure of a TI product considered for purchase by user for use in user's product would reasonably be expected to cause severe personal injury or death such as devices which are classified as FDA Class III or similar classification, then user must specifically notify TI of such intent and enter into a separate Assurance and Indemnity Agreement.

#### RADIO FREQUENCY REGULATORY COMPLIANCE INFORMATION FOR EVALUATION MODULES

Texas Instruments Incorporated (TI) evaluation boards, kits, and/or modules (EVMs) and/or accompanying hardware that is marketed, sold, or loaned to users may or may not be subject to radio frequency regulations in specific countries.

#### General Statement for EVMs Not Including a Radio

For EVMs not including a radio and not subject to the U.S. Federal Communications Commission (FCC) or Industry Canada (IC) regulations, TI intends EVMs to be used only for engineering development, demonstration, or evaluation purposes. EVMs are not finished products typically fit for general consumer use. EVMs may nonetheless generate, use, or radiate radio frequency energy, but have not been tested for compliance with the limits of computing devices pursuant to part 15 of FCC or the ICES-003 rules. Operation of such EVMs may cause interference with radio communications, in which case the user at his own expense will be required to take whatever measures may be required to correct this interference.

#### General Statement for EVMs including a radio

User Power/Frequency Use Obligations: For EVMs including a radio, the radio included in such EVMs is intended for development and/or professional use only in legally allocated frequency and power limits. Any use of radio frequencies and/or power availability in such EVMs and their development application(s) must comply with local laws governing radio spectrum allocation and power limits for such EVMs. It is the user's sole responsibility to only operate this radio in legally acceptable frequency space and within legally mandated power limitations. Any exceptions to this are strictly prohibited and unauthorized by TI unless user has obtained appropriate experimental and/or development licenses from local regulatory authorities, which is the sole responsibility of the user, including its acceptable authorization.

#### **U.S. Federal Communications Commission Compliance**

#### For EVMs Annotated as FCC - FEDERAL COMMUNICATIONS COMMISSION Part 15 Compliant

#### Caution

This device complies with part 15 of the FCC Rules. Operation is subject to the following two conditions: (1) This device may not cause harmful interference, and (2) this device must accept any interference received, including interference that may cause undesired operation. Changes or modifications could void the user's authority to operate the equipment.

#### FCC Interference Statement for Class A EVM devices

This equipment has been tested and found to comply with the limits for a Class A digital device, pursuant to part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference when the equipment is operated in a commercial environment. This equipment generates, uses, and can radiate radio frequency energy and, if not installed and used in accordance with the instruction manual, may cause harmful interference to radio communications. Operation of this equipment in a residential area is likely to cause harmful interference in which case the user will be required to correct the interference at its own expense.

#### FCC Interference Statement for Class B EVM devices

This equipment has been tested and found to comply with the limits for a Class B digital device, pursuant to part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference in a residential installation. This equipment generates, uses and can radiate radio frequency energy and, if not installed and used in accordance with the instructions, may cause harmful interference to radio communications. However, there is no guarantee that interference will not occur in a particular installation. If this equipment does cause harmful interference to radio or television reception, which can be determined by turning the equipment off and on, the user is encouraged to try to correct the interference by one or more of the following measures:

- · Reorient or relocate the receiving antenna.

- Increase the separation between the equipment and receiver.

- · Connect the equipment into an outlet on a circuit different from that to which the receiver is connected.

- · Consult the dealer or an experienced radio/TV technician for help.

### Industry Canada Compliance (English)

#### For EVMs Annotated as IC - INDUSTRY CANADA Compliant:

This Class A or B digital apparatus complies with Canadian ICES-003.

Changes or modifications not expressly approved by the party responsible for compliance could void the user's authority to operate the equipment.

#### **Concerning EVMs Including Radio Transmitters**

This device complies with Industry Canada licence-exempt RSS standard(s). Operation is subject to the following two conditions: (1) this device may not cause interference, and (2) this device must accept any interference, including interference that may cause undesired operation of the device.

## **Concerning EVMs Including Detachable Antennas**

Under Industry Canada regulations, this radio transmitter may only operate using an antenna of a type and maximum (or lesser) gain approved for the transmitter by Industry Canada. To reduce potential radio interference to other users, the antenna type and its gain should be so chosen that the equivalent isotropically radiated power (e.i.r.p.) is not more than that necessary for successful communication. This radio transmitter has been approved by Industry Canada to operate with the antenna types listed in the user guide with the maximum permissible gain and required antenna impedance for each antenna type indicated. Antenna types not included in this list, having a gain greater than the maximum gain indicated for that type, are strictly prohibited for use with this device.

#### Canada Industry Canada Compliance (French)

Cet appareil numérique de la classe A ou B est conforme à la norme NMB-003 du Canada

Les changements ou les modifications pas expressément approuvés par la partie responsable de la conformité ont pu vider l'autorité de l'utilisateur pour actionner l'équipement.

#### Concernant les EVMs avec appareils radio

Le présent appareil est conforme aux CNR d'Industrie Canada applicables aux appareils radio exempts de licence. L'exploitation est autorisée aux deux conditions suivantes : (1) l'appareil ne doit pas produire de brouillage, et (2) l'utilisateur de l'appareil doit accepter tout brouillage radioélectrique subi, même si le brouillage est susceptible d'en compromettre le fonctionnement.

#### Concernant les EVMs avec antennes détachables

Conformément à la réglementation d'Industrie Canada, le présent émetteur radio peut fonctionner avec une antenne d'un type et d'un gain maximal (ou inférieur) approuvé pour l'émetteur par Industrie Canada. Dans le but de réduire les risques de brouillage radioélectrique à l'intention des autres utilisateurs, il faut choisir le type d'antenne et son gain de sorte que la puissance isotrope rayonnée équivalente (p.i.r.e.) ne dépasse pas l'intensité nécessaire à l'établissement d'une communication satisfaisante.

Le présent émetteur radio a été approuvé par Industrie Canada pour fonctionner avec les types d'antenne énumérés dans le manuel d'usage et ayant un gain admissible maximal et l'impédance requise pour chaque type d'antenne. Les types d'antenne non inclus dans cette liste, ou dont le gain est supérieur au gain maximal indiqué, sont strictement interdits pour l'exploitation de l'émetteur.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2014, Texas Instruments Incorporated

## Important Notice for Users of EVMs Considered "Radio Frequency Products" in Japan

EVMs entering Japan are NOT certified by TI as conforming to Technical Regulations of Radio Law of Japan.

If user uses EVMs in Japan, user is required by Radio Law of Japan to follow the instructions below with respect to EVMs:

- Use EVMs in a shielded room or any other test facility as defined in the notification #173 issued by Ministry of Internal Affairs and Communications on March 28, 2006, based on Sub-section 1.1 of Article 6 of the Ministry's Rule for Enforcement of Radio Law of Japan,

- 2. Use EVMs only after user obtains the license of Test Radio Station as provided in Radio Law of Japan with respect to EVMs, or

- 3. Use of EVMs only after user obtains the Technical Regulations Conformity Certification as provided in Radio Law of Japan with respect to EVMs. Also, do not transfer EVMs, unless user gives the same notice above to the transferee. Please note that if user does not follow the instructions above, user will be subject to penalties of Radio Law of Japan.

#### http://www.tij.co.jp

【無線電波を送信する製品の開発キットをお使いになる際の注意事項】 本開発キットは技術基準適合証明を受けておりません。 本製品の ご使用に際しては、電波法遵守のため、以下のいずれかの措置を取っていただく必要がありますのでご注意ください。

- 1. 電波法施行規則第6条第1項第1号に基づく平成18年3月28日総務省告示第173号で定められた電波暗室等の試験設備でご使用いただく。

- 2. 実験局の免許を取得後ご使用いただく。

- 3. 技術基準適合証明を取得後ご使用いただく。。

なお、本製品は、上記の「ご使用にあたっての注意」を譲渡先、移転先に通知しない限り、譲渡、移転できないものとします 上記を遵守頂けない場合は、電波法の罰則が適用される可能性があることをご留意ください。日本テキサス・インスツルメンツ株式会社 東京都新宿区西新宿6丁目24番1号 西新宿三井ビル

http://www.tij.co.jp

Texas Instruments Japan Limited (address) 24-1, Nishi-Shinjuku 6 chome, Shinjuku-ku, Tokyo, Japan

# **Preface**

## **About this Document**

This document is a Technical Reference Manual for the TCl6630K2L Evaluation Module designed and developed by elnfochips Limited for Texas Instruments, Inc.

## **Notational Conventions**

This document uses the following conventions:

Program listings, program examples, and interactive displays are shown in a mono-spaced font. Examples use **bold** for emphasis, and interactive displays use bold to distinguish commands that you enter from items that the system displays (such as prompts, command output, error messages, etc.).

Square brackets ( [ and ] ) identify an optional parameter. If you use an optional parameter, you specify the information within the brackets. Unless the square brackets are in a bold typeface, do not enter the brackets themselves.

<u>Underlined, italicized non-bold</u> text in a command is used to mark place holder text that should be replaced by the appropriate value for the user's configuration.

# **Trademarks**

The Texas Instruments logo and Texas Instruments are registered trademarks of Texas Instruments. Trademarks of Texas Instruments include: TI, XDS, Code Composer, Code Composer Studio, Probe Point, Code Explorer, DSP/BIOS, RTDX, Online DSP Lab, TCI6630K2L, 66AK2Ex, 66AK2Hx, TMS320C54x, TMS320C55x, TMS320C62x, TMS320C64x, TMS320C67x, TMS320C5000, and TMS320C6000.

MS-DOS, Windows, Windows XP, and Windows NT are trademarks of Microsoft Corporation.

UNIX is a registered trademark of The Open Group in the United States and other countries.

MicroTCA and AMC (or AdvancedMC) are trademarks of PICMG.

All other brand, product names, and service names are trademarks or registered trademarks of their respective companies or organizations.

# **Document Revision History**

| Release | Chapter | Description of Change |

|---------|---------|-----------------------|

| 1.0     | All     | Initial Draft         |

|         |         |                       |

|         |         |                       |

|         |         |                       |

|         |         |                       |

# **Acronyms**

| Acronym            | Description                                         |  |

|--------------------|-----------------------------------------------------|--|

| AMC or AdvancedMC  | Advanced Mezzanine Card                             |  |

| AIL                | Antenna Interface Link                              |  |

| CCS                | Code Composer Studio                                |  |

| DDR3               | Double Data Rate 3 Interface                        |  |

| DIP                | Dual-In-Line Package                                |  |

| DSP                | Digital Signal Processor                            |  |

| DTE                | Data Terminal Equipment                             |  |

| EEPROM             | Electrically Erasable Programmable Read Only Memory |  |

| EMAC               | Ethernet Media Access Controller                    |  |

| EMIF               | External Memory Interface                           |  |

| EVM                | Evaluation Module                                   |  |

| FMC                | FPGA Mezzanine Card                                 |  |

| FPGA               | Field Programmable Gate Array                       |  |

| I2C                | Inter Integrated Circuit                            |  |

| IPMB               | Intelligent Platform Management Bus                 |  |

| IPMI               | Intelligent Platform Management Interface           |  |

| JTAG               | Joint Test Action Group                             |  |

| LED                | Light Emitting Diode                                |  |

| McBSP              | Multi Channel Buffered Serial Port                  |  |

| MCH                | MicroTCA Carrier Hub                                |  |

| MTCA or MicroTCA   | Micro Telecommunication Computing Architecture      |  |

| MMC                | Module Management Controller                        |  |

| PCIe               | PCI Express                                         |  |

| PICMG <sup>®</sup> | PCI Industrial Computer Manufacturers Group         |  |

| RFU                | Reserved for Future Use                             |  |

| SDRAM              | Synchronous Dynamic Random Access Memory            |  |

| SERDES             | Serializer-Deserializer                             |  |

| SGMII              | Serial Gigabit Media Independent Interface          |  |

| SRIO               | Serial RapidIO                                      |  |

| UART               | Universal Asynchronous Receiver/Transmitter         |  |

| USB                | Universal Serial Bus                                |  |

| XDS560v2 | Texas Instruments' XDS560v2 System Trace Emulator |

|----------|---------------------------------------------------|

| XDS200   | Texas Instruments' XDS200 Emulator                |

# **Table of Contents**

| TCIE  | VMK2LX                                                                       | 1  |

|-------|------------------------------------------------------------------------------|----|

| 1.    | OVERVIEW                                                                     | 14 |

| 1.1   | KEY FEATURES                                                                 | 14 |

| 1.2   | FUNCTIONAL OVERVIEW                                                          | 15 |

| 1.3   | BASIC OPERATION                                                              | 17 |

| 1.4   | BOOT MODE AND BOOT CONFIGURATION SWITCH SETTING                              | 19 |

| 1.5   | POWER SUPPLY                                                                 | 20 |

| 2.    | INTRODUCTION TO TCIEVMK2LX EVALUATION BOARD                                  | 21 |

| 2.1   | MEMORY MAP                                                                   | 21 |

| 2.2   | EVM BOOT MODE AND BOOT CONFIGURATION SWITCH SETTINGS                         | 35 |

| 2.3   | BOARD REVISION ID                                                            | 36 |

| 2.4   | JTAG - EMULATION OVERVIEW                                                    | 37 |

| 2.5   | CLOCK DOMAINS                                                                | 38 |

| 2.6   | I2C BOOT EEPROM / SPI NOR FLASH                                              | 40 |

| 2.7   | FPGA                                                                         | 40 |

| 2.8   | ETHERNET SWITCH                                                              | 42 |

| 2.9   | DDR3 EXTERNAL MEMORY INTERFACE                                               | 43 |

| 2.10  | 16-BIT ASYNCHRONOUS EXTERNAL MEMORY INTERFACE (EMIF-16)                      | 44 |

| 2.11  | AFE7500EVM CARD INTERFACE                                                    | 44 |

| 2.12  | PCIE INTERFACE                                                               | 45 |

| 2.13  | ANTENNA INTERFACE (AIL)                                                      | 46 |

| 2.14  | UART INTERFACE                                                               | 47 |

| 2.15  | BOARD MANAGEMENT CONTROLLER (BMC)                                            | 47 |

| 2.16  | USB3.0 INTERFACE                                                             | 50 |

| 2.17  | EXPANSION HEADER                                                             | 50 |

| 3.    | TCIEVMK2LX EVM BOARD PHYSICAL SPECIFICATIONS                                 | 51 |

| 3.1   | BOARD LAYOUT                                                                 | 51 |

| 3.2   | CONNECTOR INDEX                                                              | 52 |

| 3.2.1 | AMC1, AMC EDGE CONNECTOR                                                     | 54 |

| 3.2.2 | CN1, GPS INPUT                                                               | 56 |

| 3.2.3 | CN2, EXPANSION CONNECTOR (EMIF, SPI, I2C, GPIO, TIMI[1:0], TIMO[1:0], UART1) | 56 |

| 3.2.4 | CN3, JUMPER FOR ENABLE SIGNAL                                                | 58 |

| 3.2.5 | CN4, GIGABIT ETHERNET CONNECTOR                                              | 58 |

| 3.2.6  | CN5, SYNCHRONIZATION EVENT                          | 59 |

|--------|-----------------------------------------------------|----|

| 3.2.7  | CN6, SIM POWER VALUE SELECT HEADER                  | 59 |

| 3.2.8  | CN7, 10MHZ CLOCK INPUT                              | 60 |

| 3.2.9  | CN8, FPGA TEST CONNECTOR                            | 60 |

| 3.2.10 | CN9, JUMPER – FPGA SECTION 1                        | 60 |

| 3.2.11 | CN10, JUMPER – BMC SECTION 1                        | 60 |

| 3.2.12 | CN11, JUMPER – BMC SECTION 2                        | 61 |

| 3.2.13 | CN12, FPGA SECTION 2                                | 61 |

| 3.2.14 | CN13, JUMPER – BMC SECTION 3                        | 61 |

| 3.2.15 | CN14, FPGA JTAG CONNECTOR (FOR FACTORY USE ONLY)    | 61 |

| 3.2.16 | CN15, MCU JTAG CONNECTOR                            | 62 |

| 3.2.17 | CN16, FMC1 (AFE7500EVM CARD) INTERFACE              | 62 |

| 3.2.18 | CN17, FMC2 (AFE7500EVM CARD) INTERFACE              | 67 |

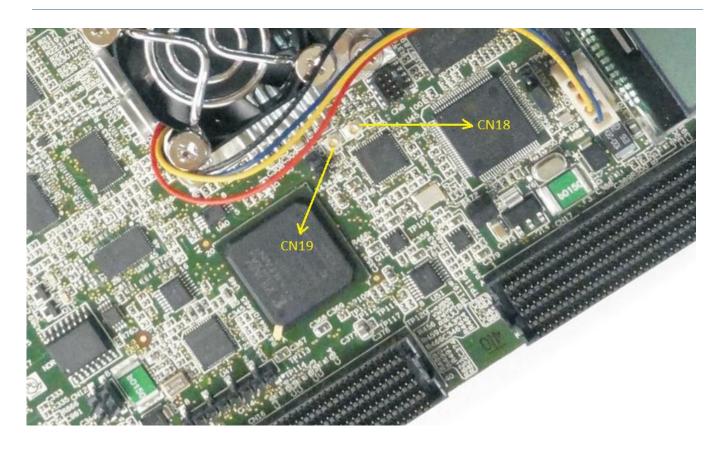

| 3.2.19 | CN18, 10MHZ CLOCK POSITIVE OUTPUT – U.FL CONNECTOR  | 72 |

| 3.2.20 | CN19, 10MHZ CLOCK NEGATIVE OUTPUT – U.FL CONNECTOR  |    |

| 3.2.21 | DC_IN1, 12V DC INPUT JACK                           | 73 |

| 3.2.22 | EMU1, TI MIPI 60-PIN SOC JTAG CONNECTOR             | 73 |

| 3.2.23 | FAN1, FAN CONNECTOR                                 | 74 |

| 3.2.24 | J1 AND J5, UART 4-PIN CONNECTORS FOR SOC AND BMC    |    |

| 3.2.25 | J2, XDS200 MINI USB CONNECTOR                       | 75 |

| 3.2.26 | J3, XDS200 MCU JTAG CONNECTOR                       | 75 |

| 3.2.27 | J4, USB3.0 TYPEA CONNECTOR                          | 76 |

| 3.2.28 | J6, MINI-USB CONNECTOR FOR UART CONSOLE             | 76 |

| 3.2.29 | PMBUS1, PMBUS FOR SMART-REFLEX CONNECTED TO UCD9090 | 76 |

| 3.2.30 | SIM1, USIM CONNECTOR                                | 77 |

| 3.3    | DIP AND PUSH BUTTON SWITCHES                        | 77 |

| 3.3.1  | PWR, FULL RESET EVENT                               | 77 |

| 3.3.2  | MCU_RST, MCU RESET EVENT                            | 78 |

| 3.3.3  | ATT, WARM RESET                                     | 78 |

| 3.3.4  | CN10, WAKE                                          | 78 |

| 3.3.5  | SW1, SOC BOOT MODE CONFIGURATIONS                   | 78 |

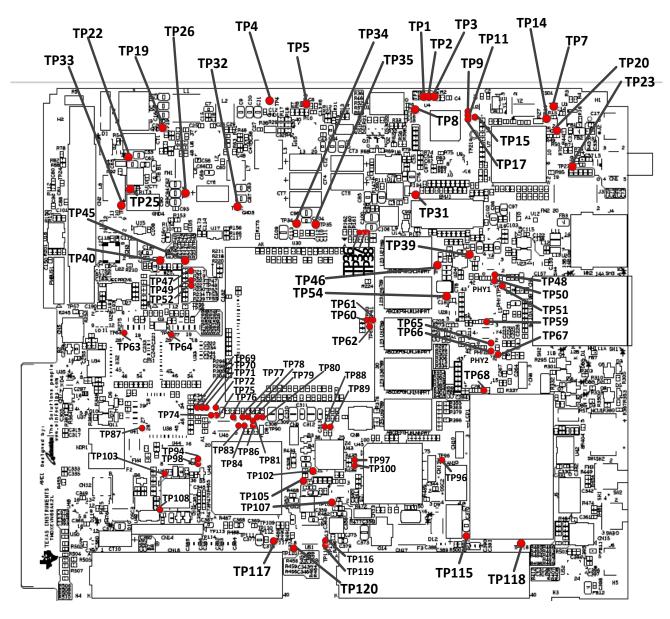

| 3.4    | TEST POINTS                                         | 79 |

| 3.5    | SYSTEM LEDS                                         | 82 |

| 4. T   | CIEVMK2LX EVM SYSTEM POWER REQUIREMENTS             | 84 |

| 11     | DOWED DECLIDEMENTS                                  | 0/ |

# TCIEVMK2LX

| 4.2     | POWER SUPPLY DISTRIBUTION                       | 86  |

|---------|-------------------------------------------------|-----|

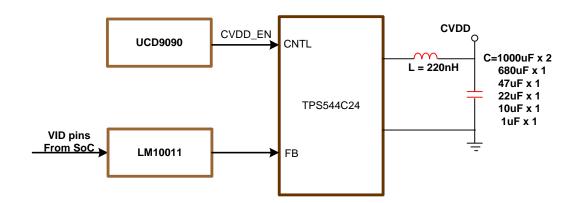

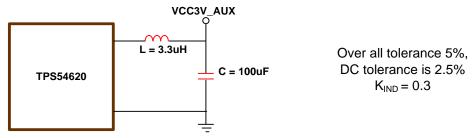

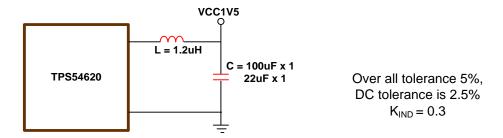

| 4.2.1   | CVDD (1V) DESIGN                                |     |

| 4.2.2   | VCC3V3_AUX AND VCC1V5 DESIGN                    | 89  |

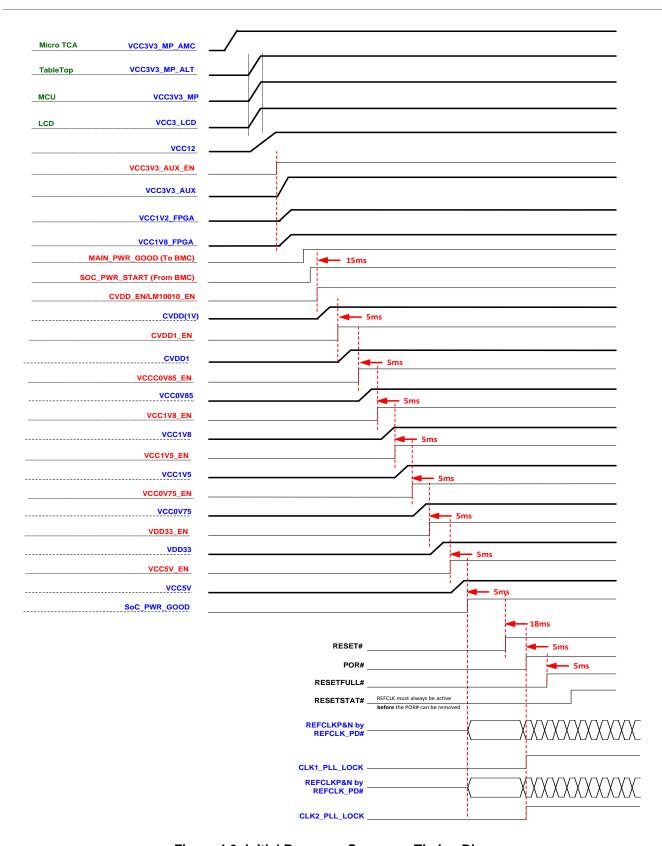

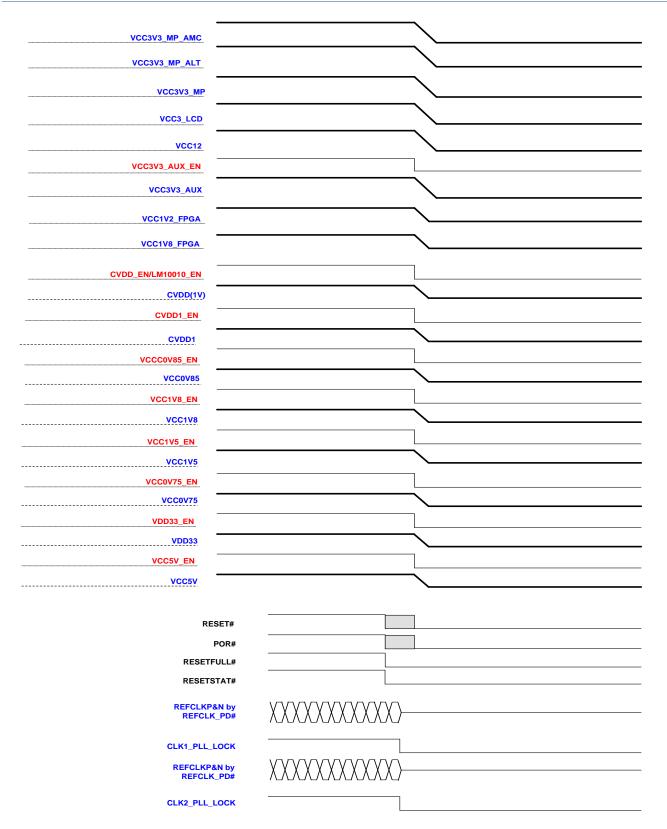

| 4.3     | POWER SUPPLY BOOT SEQUENCE                      | 90  |

| 5. T    | CIEVMK2LX FPGA FUNCTIONAL DESCRIPTION           | 95  |

| 5.1     | FPGA OVERVIEW                                   | 95  |

| 5.2     | FPGA SIGNAL DESCRIPTION                         | 95  |

| 5.3     | FPGA AFE7500EVM INTERFACE                       | 105 |

| 5.4     | BMC GPIO EXPANDER                               | 106 |

| 5.5     | TIMER CONTROL LOGIC                             | 107 |

| 5.6     | SPI PROTOCOL                                    | 107 |

| 5.6.1   | FPGA SOC/BMC PROTOCOL                           | 107 |

| 5.7     | FPGA CONFIGURATION REGISTER                     | 109 |

| 5.7.1   | FPGA CONFIGURATION REGISTER ACCESSIBLE FROM BMC | 110 |

| 5.7.1.1 | . FPGA CONFIGURATION REGISTER DESCRIPTIONS      | 111 |

| 5.7.2   | FPGA CONFIGURATION REGISTER ACCESSIBLE FROM SOC | 141 |

# **List of Figures**

| FIGURE 1.1: BLOCK DIAGRAM OF TCIEVMK2LX EVM                                 | 10  |

|-----------------------------------------------------------------------------|-----|

| FIGURE 1.2: TCIEVMK2LX EVM TOP SIDE                                         | 18  |

| FIGURE 1.3: TCIEVMK2LX EVM BOTTOM SIDE                                      | 18  |

| FIGURE 2.1: EVM BOARD REVISION                                              |     |

| FIGURE 2.2: TCIEVMK2LX EVALUATION MODULE JTAG EMULATION                     | 3   |

| FIGURE 2.3: TCIEVMK2LX EVM CLOCK DOMAINS                                    |     |

| FIGURE 2.4: TCIEVMK2LX EVALUATION MODULE (EVM) BUS DIAGRAM                  | 40  |

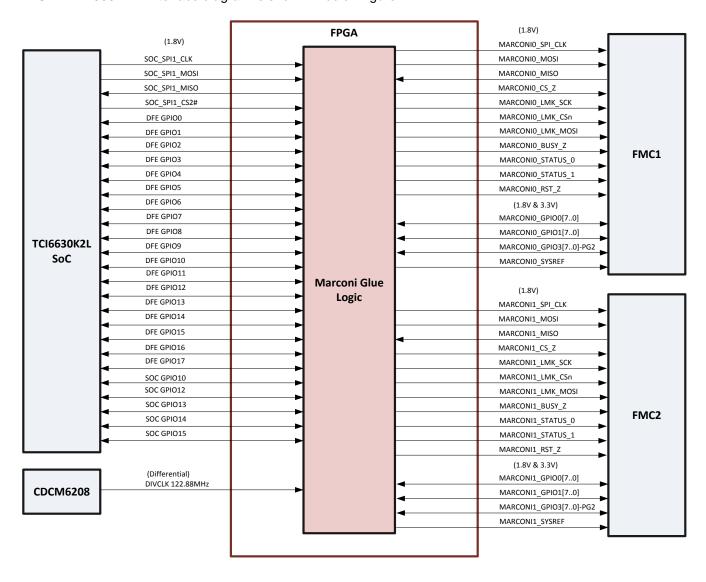

| FIGURE 2.5: TCIEVMK2LX FPGA FMC INTERFACE                                   | 42  |

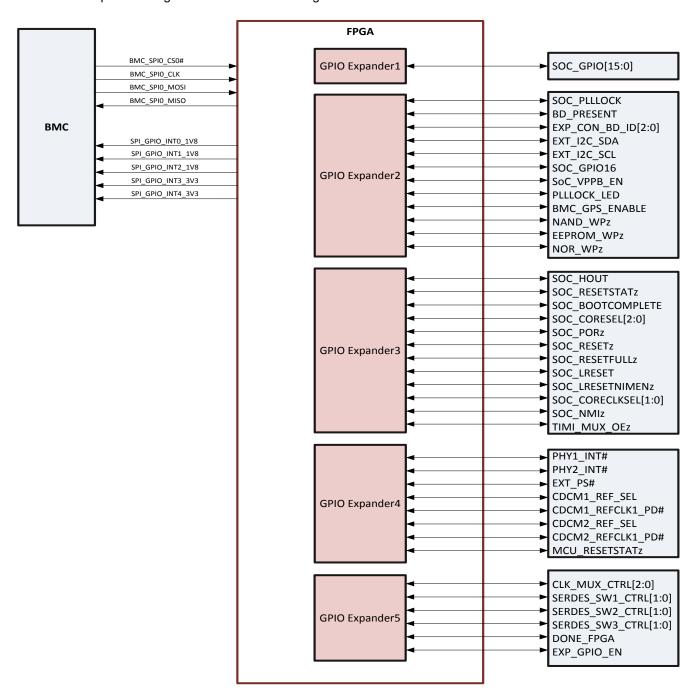

| FIGURE 2.6: TCIEVMK2LX BMC EXPANDER LOGIC                                   | 42  |

| FIGURE 2.7: TCIEVMK2LX EVM ETHERNET PHY ROUTING                             | 43  |

| FIGURE 2.8: TCIEVMK2LX EVM DDR3 INTERFACE                                   |     |

| FIGURE 2.9: TCIEVMK2LX EVM EMIF16 INTERFACE                                 |     |

| FIGURE 2.10: TCIEVMK2LX EVM AFE7500EVM CARD INTERFACES                      | 45  |

| FIGURE 2.11: TCIEVMK2LX EVM PCIE INTERFACE                                  | 40  |

| FIGURE 2.12: TCIEVMK2LX EVM AIL INTERFACE                                   | 40  |

| FIGURE 2.13: TCIEVMK2LX EVM UART CONNECTIONS                                |     |

| FIGURE 2.14: TCIEVMK2LX EVM BMC CONNECTIONS DIAGRAM                         | 49  |

| FIGURE 2.15: TCIEVMK2LX EVM USB3.0 CONNECTION DIAGRAM                       | 50  |

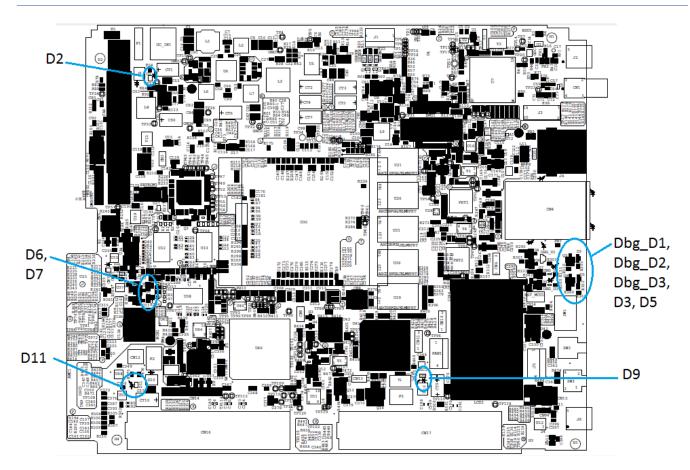

| FIGURE 3.1: TCIEVMK2LX EVM BOARD ASSEMBLY LAYOUT – TOP VIEW                 | 52  |

| FIGURE 3.2: TCIEVMK2LX EVM BOARD LAYOUT – BOTTOM VIEW                       | 52  |

| FIGURE 3.3: SYNC EVENT JUMPER SETTING                                       | 59  |

| FIGURE 3.4: SW1 DSP NO-BOOT SETTING                                         | 78  |

| Table 3.23: SW1, Boot mode configuration Switch                             | 78  |

| FIGURE 3.5: BOARD TEST POINTS (TOP)                                         | 79  |

| Figure 3.6: Board LEDs                                                      |     |

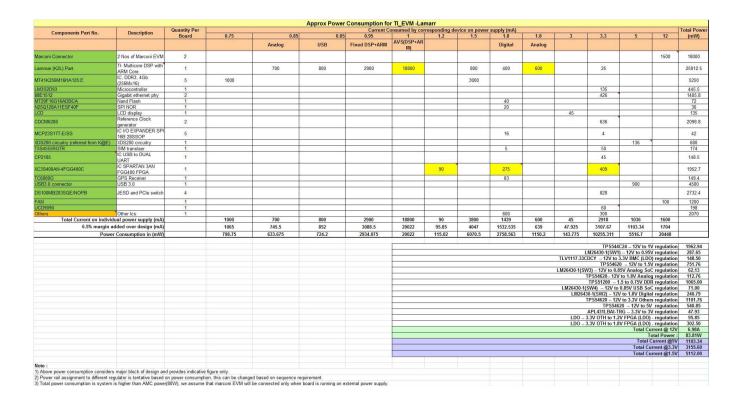

| FIGURE 4.1: TCIEVMK2LX EVM POWER CONSUMPTION                                |     |

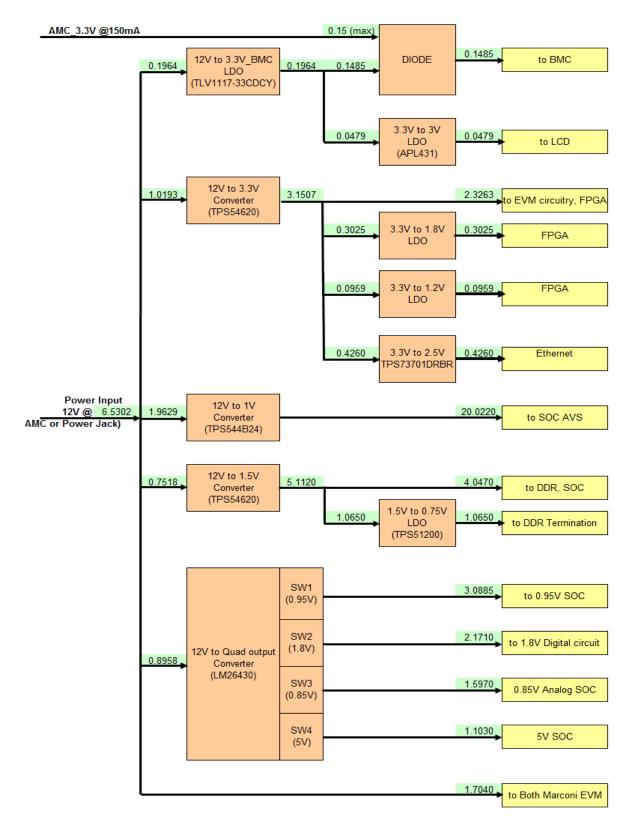

| FIGURE 4.2: TCIEVMK2LX EVM POWER GENERATION TOPOLOGY                        |     |

| FIGURE 4.3: CVDD DESIGN ON TCIEVMK2LX EVM                                   |     |

| FIGURE 4.4: VCC3V3_AUX DESIGN ON TCIEVMK2LX EVM                             |     |

| FIGURE 4.5: VCC1V5 POWER DESIGN ON TCIEVMK2LX EVM                           |     |

| FIGURE 4.6: INITIAL POWER UP SEQUENCE TIMING DIAGRAM                        |     |

| FIGURE 4.7: POWER DOWN SEQUENCE TIMING DIAGRAM                              |     |

| FIGURE 5.1: FPGA AFE7500EVM INTERFACE                                       |     |

| FIGURE 5.2: BMC GPIO EXPANDER                                               |     |

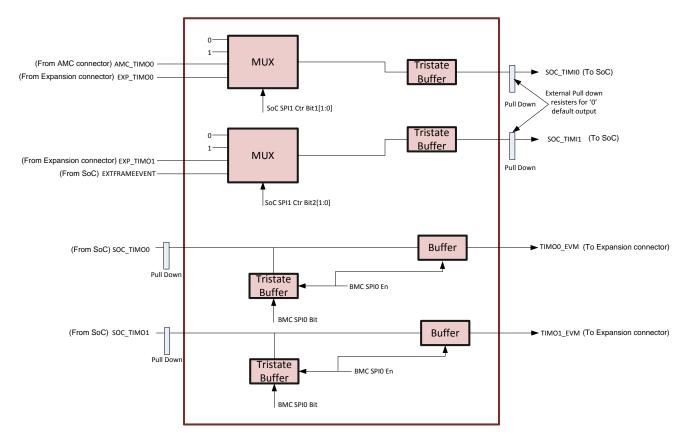

| FIGURE 5.3: TIMER CONTROL LOGIC                                             |     |

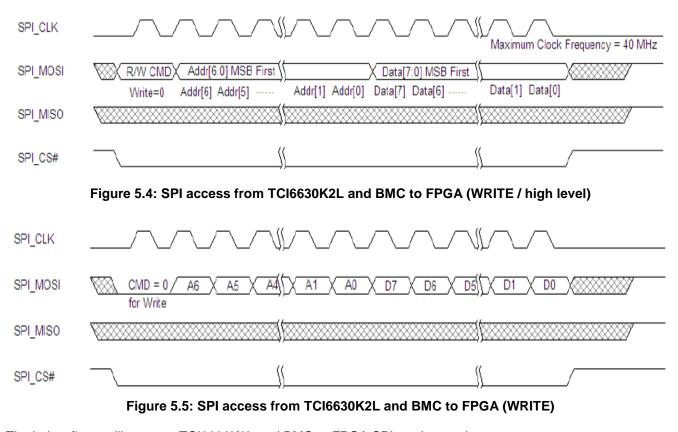

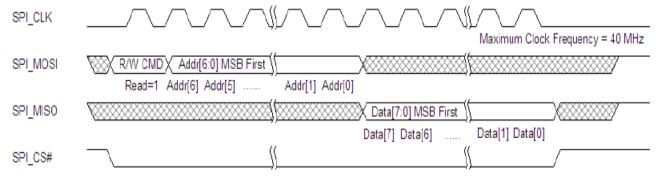

| FIGURE 5.4: SPI ACCESS FROM TCI6630K2L AND BMC TO FPGA (WRITE / HIGH LEVEL) |     |

| FIGURE 5.5: SPI ACCESS FROM TCI6630K2L AND BMC TO FPGA (WRITE)              |     |

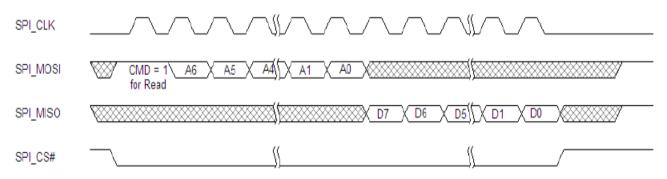

| FIGURE 5.5: SPI ACCESS FROM TCI6630K2L AND BMC TO FPGA (READ / HIGH LEVEL)  |     |

| FIGURE 5.6: SPI ACCESS FROM TCI6630K2L AND BMC TO FPGA (READ)               | 109 |

# **List of Tables**

| TABLE 2.1: TCI6630K2L MEMORY MAP                           | 22  |

|------------------------------------------------------------|-----|

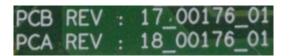

| TABLE 2.2: PCA/PCB REVISION DESCRIPTION                    | 36  |

| Table 2.3: Clock Configuration                             | 38  |

| TABLE 3.1: TCIEVMK2LX EVM BOARD CONNECTORS                 | 52  |

| TABLE 3.2: AMC EDGE CONNECTOR                              | 54  |

| TABLE 3.3: GPS INPUT CONNECTOE                             | 56  |

| TABLE 3.4: EXPANSION HEADER PIN OUT                        | 56  |

| Table 3.5: Connector Pin Out                               |     |

| TABLE 3.6: ETHERNET CONNECTOR PIN OUT                      | 58  |

| TABLE 3.7: SYNCHRONIZATION EVENT CONNECTOR PIN OUT         | 59  |

| TABLE 3.8: USIM HEADER PIN OUT                             | 59  |

| TABLE 3.9: 10MHz CLOCK INPUT CONNECTOR PIN OUT             | 60  |

| TABLE 3.10: FPGA TEST CONNECTOR PIN OUT                    | 60  |

| TABLE 3.11: CONNECTOR PIN OUT                              | 60  |

| TABLE 3.12: CONNECTOR PIN OUT                              | 60  |

| TABLE 3.13: CONNECTOR PIN OUT                              | 61  |

| TABLE 3.14: CONNECTOR PIN OUT                              | 61  |

| Table 3.15: Connector Pin Out                              |     |

| TABLE 3.16: FPGA JTAG HEADER PIN OUT                       | 61  |

| TABLE 3.17: MCU JTAG HEADER PIN OUT                        | 62  |

| Table 3.18: FMC1 Connector Pin Out                         | 62  |

| TABLE 3.19: FMC2 CONNECTOR PIN OUT                         | 67  |

| TABLE 3.20: 10MHz CLOCK OUTPUT CONNECTOR PIN OUT           | 72  |

| TABLE 3.21: 10MHz CLOCK OUTPUT CONNECTOR PIN OUT           | 73  |

| Table 3.22: MIPI 60 Connector Pin Out                      |     |

| TABLE 3.23: FAN1 CONNECTOR PIN OUT                         | 74  |

| TABLE 3.24: UART CONNECTORS PIN OUT                        | 75  |

| TABLE 3.25: XDS200 MINI USB CONNECTOR PIN OUT              |     |

| TABLE 3.26: XDS200 MCU JTAG CONNECTOR PIN OUT              | 75  |

| Table 3.27: USB3.0 Connector Pin Out                       |     |

| TABLE 3.28: MINI USB CONNECTOR PIN OUT                     | 76  |

| Table 3.29: PMBUS Connector Pin Out                        |     |

| Table 3.30: USIM Connector Pin Out                         |     |

| TABLE 3.31: TCIEVMK2LX EVM BOARD SWITCHES                  |     |

| TABLE 3.33: TCIEVMK2LX EVM BOARD TEST POINTS               | 80  |

| TABLE 3.34: TCIEVMK2LX EVM BOARD LEDS                      |     |

| TABLE 4.1: CURRENT CONSUMPTION ON EACH VOLTAGE RAIL        |     |

| TABLE 4.2: POWER-UP AND DOWN TIMING ON TCIEVMK2LX EVM      | 91  |

| TABLE 5.1: PIN TYPE NOTATION INTERPRETATION                | 95  |

| TABLE 5.2: TCIEVMK2LX EVM FPGA PIN DESCRIPTION             | 95  |

| Table 5.3: BMC FPGA Pin Description                        |     |

| Table 5.4: TCI6630K2L EVM FPGA PIN DESCRIPTION             |     |

| TABLE 5.5: BMC FPGA CONFIGURATION REGISTERS SUMMARY        |     |

| TABLE 5.6: TCI6630K2L FPGA CONFIGURATION REGISTERS SUMMARY | 141 |

## 1. Overview

This chapter provides an overview of the TCIEVMK2LX Evaluation Module (EVM) along with the key features and block diagram.

- 1.1 Key Features

- 1.2 Functional Overview

- 1.3 Basic Operation

- 1.4 Configuration Switch Settings

- 1.5 Power Supply

# 1.1 Key Features

The TCIEVMK2LX Evaluation Module (EVM) is a high performance, cost-efficient, standalone development platform that enables users to evaluate and develop applications for the Texas Instruments' Keystone II SoC. The TCIEVMK2LX Evaluation Module (EVM) also serves as a hardware reference design platform for the TCI6630K2L SoC. The EVM's form-factor is equivalent to a Double-wide PICMG® AMC.0 R2.0 AdvancedMC module.

Schematics, code examples and application notes are available, to ease the hardware development process and to reduce the time to market.

The key features of TCIEVMK2LX Evaluation Module (EVM) are:

- Texas instrument's Four DSP Core + Two ARM Core SoC

- 2 GB ECC DDR3 1600

- 512 MB of NAND Flash

- 128 MB of NOR Flash

- Four Gigabit Ethernet ports supporting 10/100/1000 Mbps data-rate two on AMC connector and two RJ-45 connector

- 170 pin B+ style AMC Interface containing PCIe, SGMII, AIL

- Two FMC Connector for AFE7500EVM Interface containing high speed 4 JESD pairs and 2 JESD pairs

- One host USB3.0 port

- 128 KB I2C EEPROM for booting

- 4 User Indication LEDs, 1 Banks of DIP Switches

- Two RS232 serial interface on 4-Pin header or UART over USB miniB

- Timer, SPI,UART,I2C,GPIO,EMIF interfaces on 120-pin expansion header

- Supports On Board Emulation (XDS200) as well as External Emulator

- Supports External Emulator (i.e. XDS560) through MIPI 60-Pin connector

- Powered by DC power-brick adaptor (12V/7A) or AMC Carrier back-plane

- High-speed DSP interconnect enabled by Gigabit EMAC interfaces

- One USIM interface

- One GPS module on board

- One LCD display for debugging states

- RoHS Compliant Design

- Double wide PICMG ® AdvancedMC (AMC) form factor (7.11" x 5.84")

- Board Management Controller (BMC) for Intelligent Platform Management Interface (IPMI)

## 1.2 Functional Overview

The TCIEVMK2LX Evaluation Module (EVM) contains TCI6630K2L SoC platform. TCI6630K2L device is based on industry's leading high performance multi core Keystone II architecture. It has Four TMS320C66x™ DSP Core and Two ARM Cortex™-A15 MPCore™ Processors. TCI6630K2L is a low-power baseband solution with integrated digital front end (DFE) that meets the more stringent power, size, and cost requirements of small cell wireless base stations. This device's ARM and DSP cores deliver exceptional processing power on platforms for developing all wireless standards including WCDMA/HSPA/HSPA+, TD-SCDMA, GSM, TDD-LTE, FDD-LTE, and WiMAX.

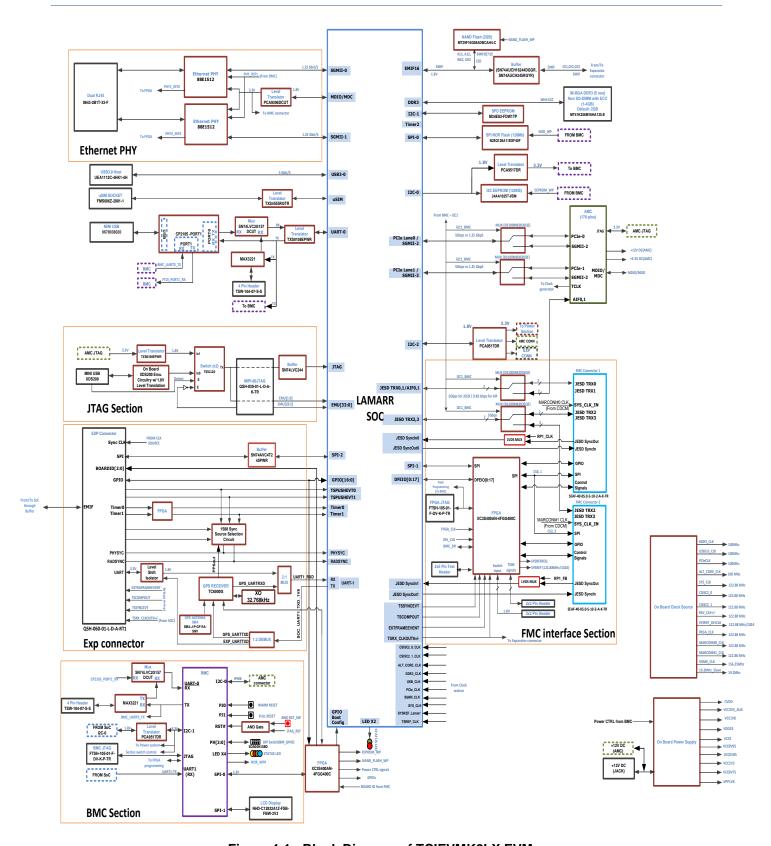

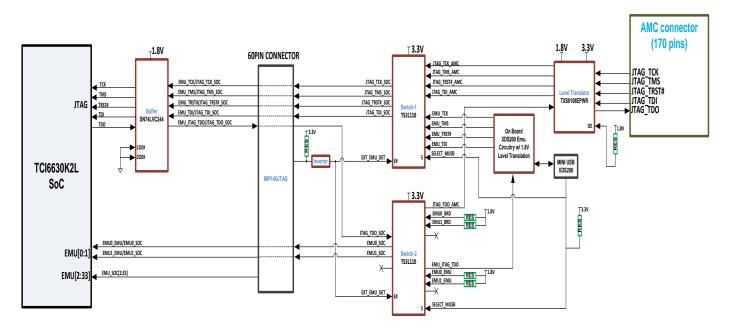

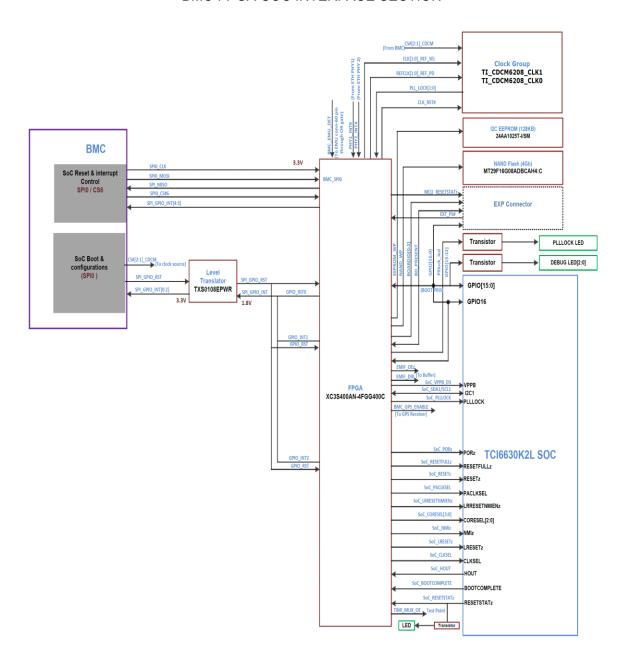

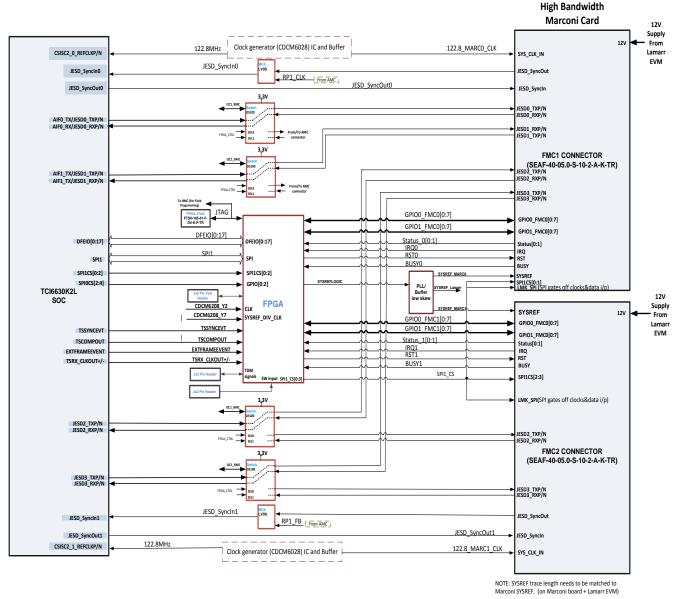

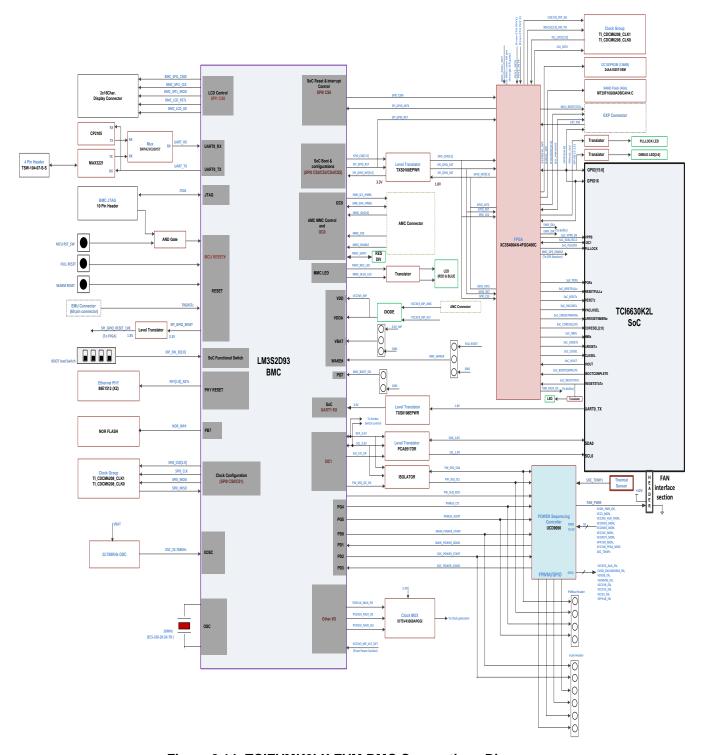

The functional block diagram of TCIEVMK2LX Evaluation Module (EVM) is shown in below figure:

Figure 1.1: Block Diagram of TCIEVMK2LX EVM

# 1.3 Basic Operation

The TCIEVMK2LX EVM platform is designed to work with TI's Code Composer Studio (CCS) development environment and ships with a version specifically tailored for this board. CCS can interfaces with the board via on-board emulation circuitry using the USB cable supplied along with this EVM or through external emulator.

The EVM comes with the Texas Instruments Multicore Software Development Kit (MCSDK) for SYS/BIOS OS. The BIOS MCSDK provides the core foundational building blocks that facilitate application software development on TI's high performance and multicore DSPs. It also includes U-Boot, Kernel, File System and Matrix Demo. Follow the instruction in BIOS MCSDK Getting Started Guide to install all the necessary development tools, drivers and documentation.

To start operating the board, follow instructions given in the Quick Start Guide. This guide provides instructions for proper connections and configuration for booting Linux kernel and running the Matrix Demo. After completing the Matrix Demo, proceed with installations of CCS and the EVM support files by following the instructions given in the Flash Drive. This process will install all the necessary development tools, drivers and documentation.

After the installation is completed, follow below steps to run Code Composer Studio.

- 1. Power ON the board using power brick adaptor (12V/7A) supplied along with this EVM.

- 2. Connect USB cable from host PC to EVM board.

- 3. Launch Code Composer Studio from host PC by double clicking on its icon at PC desktop.

Detailed information about the EVM including examples and reference material is available in the Flash Drive available with this EVM kit.

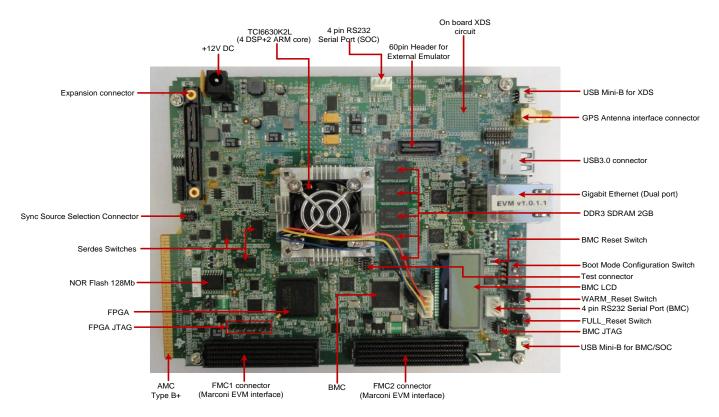

Figure 1.2: TCIEVMK2LX EVM Top Side

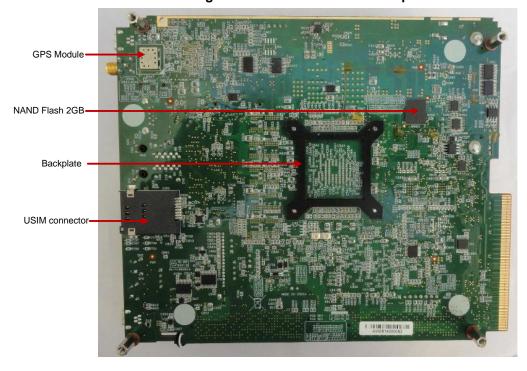

Figure 1.3: TCIEVMK2LX EVM Bottom Side

# 1.4 Boot Mode and Boot Configuration Switch Setting

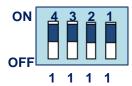

The TCIEVMK2LX EVM has 4 sliding DIP switches (Board Ref. SW1) to determine boot mode, boot configuration, device number, Endian mode, CorePac PLL clock, JESD mode slection and PCIe mode selection. Mode selection options latch at every reset of the DSP. Please refer Table 3.23 for Boot mode configuration settings.

# 1.5 Power Supply

TCIEVMK2LX Evaluation Module (EVM) can be powered from a single +12V / 7A DC (84W) external power supply connected to DC power jack (DC\_IN1). +12V input is converted into required voltage levels using on board DC-DC converters.

- +0.8 +1.1 V is Smart Reflex enabled DSP core variable supply voltage

- +0.95V is used for DSP core fixed supply voltage and internal memory

- +1.5V is used for DDR3 I/O of SoC and DDR3 chips

- +0.75V is DDR3 reference voltage supply

- +0.85V is used for SerDes analog power supply voltage

- +0.85V is used for USB LV PHY power supply voltage

- +1.8V is used for SerDes I/O, Core PLL, DDR3 DLL and FPGA I/O

- +2.5V is used for Gigabit Ethernet PHY

- +3.3V is used for FPGA I/O, microcontroller and other on board circuit

- +1.2V is used for FPGA Core and Gigabit Ethernet PHY core

- +5.0V is used for USB power supply and XDS circuit

- +12V used to power up FMC card

The TCIEVMK2LX Evaluation Module (EVM) can also be powered up from the AMC edge connector (AMC1). If the board is inserted into a PICMG® AMC.0 R2.0 compliant system chassis or AMC Carrier back-plane, an external +12V supply from DC jack (DC\_IN1) is not required.

#### Note:

External Power Supply Requirements: Nom Voltage: 12 VDC

Max Current: 7000 mA Efficiency Level V

External Power Supply Regulatory Compliance Certifications: Recommend selection and use of an external a power supply which meets TI's required minimum electrical ratings in addition to complying with applicable regional product regulatory/safety certification requirements such as (by example) UL, CSA, VDE, CCC, PSE, etc.

# 2. Introduction to TCIEVMK2LX Evaluation board

This chapter provides an introduction and details of interfaces for the TCIEVMK2LX EVM board. It contains:

- 2.1 Memory Map

- 2.2 EVM Boot mode and Boot configuration switch settings

- 2.3 Board Revision ID

- 2.4 JTAG Emulation Overview

- 2.5 Clock Domains

- 2.6 I2C boot EEPROM/ SPI NOR Flash

- 2.7 FPGA

- 2.8 Gigabit Ethernet PHY

- 2.9 DDR3 External Memory Interface

- 2.10 NAND Flash Interface

- 2.11 AFE7500EVM Card Interface

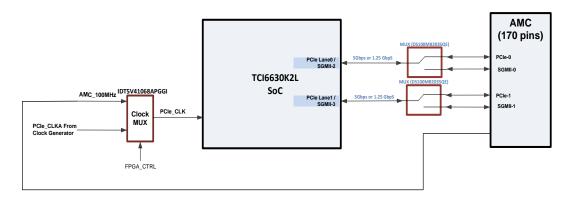

- 2.12 PCIe Interface

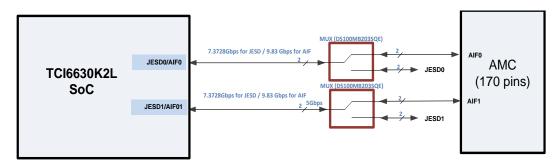

- 2.13 Antenna Interface (AIL)

- 2.14 UART Interface

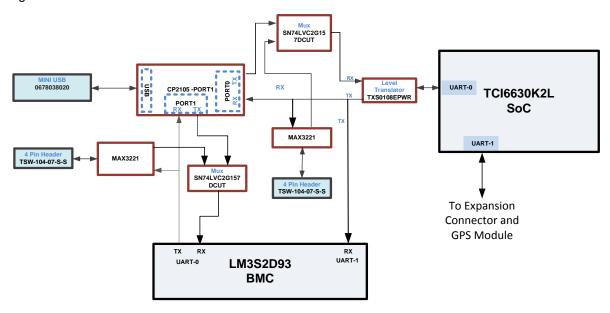

- 2.15 Board Management Controller for IPMI

- 2.16 USB3.0 Interface

- 2.17 Expansion Header

# 2.1 Memory Map

The memory map of the TCI6630K2L device is as shown in Table 2.1.

Table 2.1: TCI6630K2L Memory Map

| Physical 40   | bit Address  |         |                                   |                        |                        |

|---------------|--------------|---------|-----------------------------------|------------------------|------------------------|

| Start         | End          | Bytes   | ARM View                          | DSP View               | SOC View               |

| 00 0000 0000  | 00 0003 FFFF | 256K    | ARM ROM                           | Reserved               | ARM ROM                |

| 00 0004 0000  | 00 007F FFFF | 8M-256K | Reserved                          | Reserved               | Reserved               |

| 00 0080 0000  | 00 008F FFFF | 1M      | Reserved                          | L2 SRAM                | L2 SRAM                |

| 00 0090 0000  | 00 00DF FFFF | 5M      | Reserved                          | Reserved               | Reserved               |

| 00 00E0 0000  | 00 00E0 7FFF | 32K     | Reserved                          | L1P SRAM               | L1P SRAM               |

| 00 00E0 8000  | 00 00EF FFFF | 1M-32K  | Reserved                          | Reserved               | Reserved               |

| 00 00F0 0000  | 00 00F0 7FFF | 32K     | Reserved                          | L1D SRAM               | L1D SRAM               |

| 00 00F0 8000  | 00 00FF FFFF | 1M-32K  | Reserved                          | Reserved               | Reserved               |

| 00 0100 0000  | 00 0100 FFFF | 64K     | ARM AXI2VBUSM Master<br>Registers | C66x CorePac registers | C66x CorePac registers |

| 00 0101 0000  | 00 010F FFFF | 1M-64K  | Reserved                          | C66x CorePac registers | C66x CorePac registers |

| 00 0110 0000  | 00 0110 FFFF | 64K     | ARM STM Stimulus Ports            | C66x CorePac registers | C66x CorePac registers |

| 00 0111 0000  | 00 01BF FFFF | 11M-64K | Reserved                          | C66x CorePac registers | C66x CorePac registers |

| 00 01C0 0000  | 00 01CF FFFF | 1M      | Reserved                          | Reserved               | Reserved               |

| 00 01 D0 0000 | 00 01D0 007F | 128     | Tracer CFG0                       | Tracer CFG0            | Tracer CFG0            |

| 00 01 D0 0080 | 00 01D0 7FFF | 32K-128 | Reserved                          | Reserved               | Reserved               |

| 00 01 D0 8000 | 00 01D0 807F | 128     | Tracer CFG1                       | Tracer CFG1            | Tracer CFG1            |

| 00 01D0 8080  | 00 01D0 FFFF | 32K-128 | Reserved                          | Reserved               | Reserved               |

| 00 01D1 0000  | 00 01D1 007F | 128     | Tracer CFG2                       | Tracer CFG2            | Tracer CFG2            |

| 00 01D1 0080  | 00 01D1 7FFF | 32K-128 | Reserved                          | Reserved               | Reserved               |

| 00 01D1 8000  | 00 01D1 807F | 128     | Tracer CFG3                       | Tracer CFG3            | Tracer CFG3            |

| 00 01D1 8080  | 00 01D1 FFFF | 32K-128 | Reserved                          | Reserved               | Reserved               |

| 00 01D2 0000  | 00 01D2 007F | 128     | Tracer CFG23                      | Tracer CFG23           | Tracer CFG23           |

| 00 01D2 0080  | 00 01D2 7FFF | 32K-128 | Reserved                          | Reserved               | Reserved               |

| 00 01D2 8000  | 00 01D2 807F | 128     | Tracer CFG8                       | Tracer CFG8            | Tracer CFG8            |

| 00 01D2 8080  | 00 01D2 FFFF | 32K-128 | Reserved                          | Reserved               | Reserved               |

| 00 01D3 0000  | 00 01D3 007F | 128     | Tracer CFG20                      | Tracer CFG20           | Tracer CFG20           |

| 00 01D3 0080  | 00 01D3 7FFF | 32K-128 | Reserved                          | Reserved               | Reserved               |

| 00 01D3 8000  | 00 01D3 807F | 128     | Tracer CFG21                      | Tracer CFG21           | Tracer CFG21           |

| 00 01D3 8080  | 00 01D3 FFFF | 32K-128 | Reserved                          | Reserved               | Reserved               |

| 00 01 D4 0000 | 00 01D4 007F | 128     | Tracer CFG25                      | Tracer CFG25           | Tracer CFG25           |

| 00 01 D4 0080 | 00 01D4 7FFF | 32K-128 | Reserved                          | Reserved               | Reserved               |

| 00 01 D4 8000 | 00 01D4 807F | 128     | Tracer CFG09                      | Tracer CFG09           | Tracer CFG09           |

| 00 01D4 8080  | 00 01D4 FFFF | 32K-128 | Reserved                          | Reserved               | Reserved               |

| 00 01D5 0000  | 00 01D5 007F | 128     | Tracer CFG10                      | Tracer CFG10           | Tracer CFG10           |

| 00 01D5 0080  | 00 01D5 7FFF | 32K-128 | Reserved                          | Reserved               | Reserved               |

| 00 01D5 8000  | 00 01D5 807F | 128     | Tracer CFG11                      | Tracer CFG11           | Tracer CFG11           |

| 00 01D5 8080  | 00 01D5 FFFF | 32K-128 | Reserved                          | Reserved               | Reserved               |

| 00 01D6 0000  | 00 01D6 007F | 128     | Tracer CFG12                      | Tracer CFG12           | Tracer CFG12           |

| Physical 40  | bit Address   |         |              |              |              |

|--------------|---------------|---------|--------------|--------------|--------------|

| Start        | End           | Bytes   | ARM View     | DSP View     | SOC View     |

| 00 01D6 0080 | 00 01D6 7FFF  | 32K-128 | Reserved     | Reserved     | Reserved     |

| 00 01D6 8000 | 00 01D6 807F  | 128     | Reserved     | Reserved     | Reserved     |

| 00 01D6 8080 | 00 01D6 FFFF  | 32K-128 | Reserved     | Reserved     | Reserved     |

| 00 01D7 0000 | 00 01D7 007F  | 128     | Reserved     | Reserved     | Reserved     |

| 00 01D7 0080 | 00 01D7 7FFF  | 32K-128 | Reserved     | Reserved     | Reserved     |

| 00 01D7 8000 | 00 01D7 807F  | 128     | Reserved     | Reserved     | Reserved     |

| 00 01D7 8080 | 00 01D7 FFFF  | 32K-128 | Reserved     | Reserved     | Reserved     |

| 00 01D8 0000 | 00 01D8 007F  | 128     | Reserved     | Reserved     | Reserved     |

| 00 01D8 0080 | 00 01D8 7FFF  | 32K-128 | Reserved     | Reserved     | Reserved     |

| 00 01D8 8000 | 00 01D8 807F  | 128     | Tracer CFG26 | Tracer CFG26 | Tracer CFG26 |

| 00 01D8 8080 | 00 01D8 8FFF  | 32K-128 | Reserved     | Reserved     | Reserved     |

| 00 01D9 0000 | 00 01D9 007F  | 128     | Tracer CFG27 | Tracer CFG27 | Tracer CFG28 |

| 00 01D9 0080 | 00 01D9 7FFF  | 32K-128 | Reserved     | Reserved     | Reserved     |

| 00 01D9 8000 | 00 01D9 807F  | 128     | Tracer CFG28 | Tracer CFG28 | Tracer CFG28 |

| 00 01D9 8080 | 00 01D9 FFFF  | 32K-128 | Reserved     | Reserved     | Reserved     |

| 00 01DA 0000 | 00 01DA 007F  | 128     | Tracer CFG22 | Tracer CFG22 | Tracer CFG22 |

| 00 01DA 0080 | 00 01DA 7FFF  | 32K-128 | Reserved     | Reserved     | Reserved     |

| 00 01DA 8000 | 00 01DA 807F  | 128     | Reserved     | Reserved     | Reserved     |

| 00 01DA 8080 | 00 01DA FFFF  | 32K-128 | Reserved     | Reserved     | Reserved     |

| 00 01DB 0000 | 00 01 DB 007F | 128     | Tracer CFG31 | Tracer CFG31 | Tracer CFG31 |

| 00 01DB 0080 | 00 01DB 7FFF  | 32K-128 | Reserved     | Reserved     | Reserved     |

| 00 01DB 8000 | 00 01DB 807F  | 128     | Reserved     | Reserved     | Reserved     |

| 00 01DB 8080 | 00 01DB 8FFF  | 32K-128 | Reserved     | Reserved     | Reserved     |

| 00 01DC 0000 | 00 01DC 007F  | 128     | Tracer CFG17 | Tracer CFG17 | Tracer CFG17 |

| 00 01DC 0080 | 00 01DC 7FFF  | 32K-128 | Reserved     | Reserved     | Reserved     |

| 00 01DC 8000 | 00 01DC 807F  | 128     | Tracer CFG18 | Tracer CFG18 | Tracer CFG18 |

| 00 01DC 8080 | 00 01DC FFFF  | 32K-128 | Reserved     | Reserved     | Reserved     |

| 00 01DD 0000 | 00 01DD 007F  | 128     | Tracer CFG19 | Tracer CFG19 | Tracer CFG19 |

| 00 01DD 0080 | 00 01DD 7FFF  | 32K-128 | Reserved     | Reserved     | Reserved     |

| 00 01DD 8000 | 00 01DD 807F  | 128     | Tracer CFG4  | Tracer CFG4  | Tracer CFG4  |

| 00 01DD 8080 | 00 01DD FFFF  | 32K-128 | Reserved     | Reserved     | Reserved     |

| 00 01DE 0000 | 00 01DE 007F  | 128     | Tracer CFG5  | Tracer CFG5  | Tracer CFG5  |

| 00 01DE 0080 | 00 01DE 03FF  | 1K-128  | Reserved     | Reserved     | Reserved     |

| 00 01DE 0400 | 00 01DE 047F  | 128     | Tracer CFG6  | Tracer CFG6  | Tracer CFG6  |

| 00 01DD 0480 | 00 01DD 07FF  | 1K-128  | Reserved     | Reserved     | Reserved     |

| 00 01DE 0800 | 00 01DE 087F  | 128     | Tracer CFG7  | Tracer CFG7  | Tracer CFG7  |

| 00 01DE 0880 | 00 01DE 7FFF  | 30K-128 | Reserved     | Reserved     | Reserved     |

| 00 01DE 8000 | 00 01DE 807F  | 128     | Tracer CFG24 | Tracer CFG24 | Tracer CFG24 |

| 00 01DE 8080 | 00 01DF FFFF  | 64K-128 | Reserved     | Reserved     | Reserved     |

| 00 01E0 0000 | 00 01E3 FFFF  | 256K    | Reserved     | Reserved     | Reserved     |

| 00 01E4 0000 | 00 01E4 3FFF  | 16K     | Reserved     | Reserved     | Reserved     |

| 00 01E4 4000 | 00 01E7 FFFF  | 240k    | Reserved     | Reserved     | Reserved     |

| Physical 40  | ) bit Address |         |                                              |                                              |                                              |

|--------------|---------------|---------|----------------------------------------------|----------------------------------------------|----------------------------------------------|

| Start        | End           | Bytes   | ARM View                                     | DSP View                                     | SOC View                                     |

| 00 01E8 0000 | 00 01E8 3FFF  | 16K     | ARM CorePac VBUSP Memory<br>Mapped Registers | ARM CorePac VBUSP Memory<br>Mapped Registers | ARM CorePac VBUSP<br>Memory Mapped Registers |

| 00 01E8 4000 | 00 01EB FFFF  | 240k    | Reserved                                     | Reserved                                     | Reserved                                     |

| 00 01EC 0000 | 00 01EF FFFF  | 256K    | Reserved                                     | Reserved                                     | Reserved                                     |

| 00 01F0 0000 | 00 01F7 FFFF  | 512K    | Reserved                                     | Reserved                                     | Reserved                                     |

| 00 01F8 0000 | 00 01F8 FFFF  | 64K     | Reserved                                     | Reserved                                     | Reserved                                     |

| 00 01F9 0000 | 00 01F9 FFFF  | 64K     | Reserved                                     | Reserved                                     | Reserved                                     |

| 00 01FA 0000 | 00 01FB FFFF  | 128K    | Reserved                                     | Reserved                                     | Reserved                                     |

| 00 01FC 0000 | 00 01FD FFFF  | 128K    | Reserved                                     | Reserved                                     | Reserved                                     |

| 00 01FE 0000 | 00 01FF FFFF  | 128K    | Reserved                                     | Reserved                                     | Reserved                                     |

| 00 0200 0000 | 00 020F FFFF  | 1M      | Reserved                                     | Reserved                                     | Reserved                                     |

| 00 0210 0000 | 00 0210 FFFF  | 64K     | RAC - FEI configuration                      | RAC - FEI configuration                      | RAC - FEI configuration                      |

| 00 0211 0000 | 00 0211 FFFF  | 64K     | RAC - BEI configuration                      | RAC - BEI configuration                      | RAC - BEI configuration                      |

| 00 0212 0000 | 00 0213 FFFF  | 128K    | RAC - GCCP 0 configuration                   | RAC - GCCP 0 configuration                   | RAC - GCCP 0 configuration                   |

| 00 0214 0000 | 00 0215 FFFF  | 128K    | RAC - GCCP 1 configuration                   | RAC - GCCP 1 configuration                   | RAC - GCCP 1 configuration                   |

| 00 0216 0000 | 00 0217 FFFF  | 128K    | Reserved                                     | Reserved                                     | Reserved                                     |

| 00 0218 0000 | 00 0218 7FFF  | 32k     | Reserved                                     | Reserved                                     | Reserved                                     |

| 00 0218 8000 | 00 0218 FFFF  | 32k     | Reserved                                     | Reserved                                     | Reserved                                     |

| 00 0219 0000 | 00 0219 FFFF  | 64k     | Reserved                                     | Reserved                                     | Reserved                                     |

| 00 021A 0000 | 00 021A FFFF  | 64K     | Reserved                                     | Reserved                                     | Reserved                                     |

| 00 021B 0000 | 00 021B FFFF  | 64K     | Reserved                                     | Reserved                                     | Reserved                                     |

| 00 021C 0000 | 00 021C 03FF  | 1K      | TCP3d_0 configuration                        | TCP3d_0 configuration                        | TCP3d_0 configuration                        |

| 00 021C 0400 | 00 021C 3FFF  | 15K     | Reserved                                     | Reserved                                     | Reserved                                     |

| 00 021C 4000 | 00 021C 43FF  | 1K      | Reserved                                     | Reserved                                     | Reserved                                     |

| 00 021C 4400 | 00 021C 5FFF  | 7K      | Reserved                                     | Reserved                                     | Reserved                                     |

| 00 021C 6000 | 00 021C 63FF  | 1K      | Reserved                                     | Reserved                                     | Reserved                                     |

| 00 021C 6400 | 00 021C 7FFF  | 7K      | Reserved                                     | Reserved                                     | Reserved                                     |

| 00 021C 8000 | 00 021C 83FF  | 1K      | TCP3d_1 configuration                        | TCP3d_1 configuration                        | TCP3d_1 configuration                        |

| 00 021C 8400 | 00 021C FFFF  | 31K     | Reserved                                     | Reserved                                     | Reserved                                     |

| 00 021D 0000 | 00 021D 00FF  | 256     | VCP2_0 configuration                         | VCP2_0 configuration                         | VCP2_0 configuration                         |

| 00 021D 0100 | 00 021D 3FFF  | 16K     | Reserved                                     | Reserved                                     | Reserved                                     |

| 00 021D 4000 | 00 021D 40FF  | 256     | VCP2_1 configuration                         | VCP2_1 configuration                         | VCP2_1 configuration                         |

| 00 021D 4100 | 00 021D 7FFF  | 16K     | Reserved                                     | Reserved                                     | Reserved                                     |

| 00 021D 8000 | 00 021D 80FF  | 256     | VCP2_2 configuration                         | VCP2_2 configuration                         | VCP2_2 configuration                         |

| 00 021D 8100 | 00 021D BFFF  | 16K     | Reserved                                     | Reserved                                     | Reserved                                     |

| 00 021D C000 | 00 021D C0FF  | 256     | VCP2_3 configuration                         | VCP2_3 configuration                         | VCP2_3 configuration                         |

| 00 021D C100 | 00 021D EFFF  | 12K-256 | Reserved                                     | Reserved                                     | Reserved                                     |

| 00 021D F000 | 00 021D F07F  | 128     | Reserved                                     | Reserved                                     | Reserved                                     |

| 00 021D F080 | 00 021D FFFF  | 4K-128  | Reserved                                     | Reserved                                     | Reserved                                     |

| 00 021E 0000 | 00 021E FFFF  | 64K     | Reserved                                     | Reserved                                     | Reserved                                     |

| 00 021F 0000 | 00 021F 07FF  | 2K      | FFTC_0 configuration                         | FFTC_0 configuration                         | FFTC_0 configuration                         |

| 00 021F 0800 | 00 021F 0FFF  | 2K      | Reserved                                     | Reserved                                     | Reserved                                     |

| 00 021F 1000 | 00 021F 17FF  | 2K      | Reserved                                     | Reserved                                     | Reserved                                     |

| Physical 40  | ) bit Address |          |                      |                      |                      |

|--------------|---------------|----------|----------------------|----------------------|----------------------|

| Start        | End           | Bytes    | ARM View             | DSP View             | SOC View             |

| 00 021F 1800 | 00 021F 3FFF  | 10K      | Reserved             | Reserved             | Reserved             |

| 00 021F 4000 | 00 021F 47FF  | 2K       | FFTC_1 configuration | FFTC_1 configuration | FFTC_1 configuration |

| 00 021F 4800 | 00 021F 7FFF  | 14K      | Reserved             | Reserved             | Reserved             |

| 00 021F 8000 | 00 021F 87FF  | Reserved | Reserved             | Reserved             | Reserved             |

| 00 021F 8800 | 00 021F BFFF  | Reserved | Reserved             | Reserved             | Reserved             |

| 00 021F C000 | 00 021F C7FF  | Reserved | Reserved             | Reserved             | Reserved             |

| 00 021F C800 | 00 021F FFFF  | 14K      | Reserved             | Reserved             | Reserved             |

| 00 0220 0000 | 00 0220 007F  | 128      | Timer0               | Timer0               | Timer0               |

| 00 0220 0080 | 00 0220 FFFF  | 64K-128  | Reserved             | Reserved             | Reserved             |

| 00 0221 0000 | 00 0221 007F  | 128      | Timer1               | Timer1               | Timer1               |

| 00 0221 0080 | 00 0221 FFFF  | 64K-128  | Reserved             | Reserved             | Reserved             |

| 00 0222 0000 | 00 0222 007F  | 128      | Timer2               | Timer2               | Timer2               |

| 00 0222 0080 | 00 0222 FFFF  | 64K-128  | Reserved             | Reserved             | Reserved             |

| 00 0223 0000 | 00 0223 007F  | 128      | Timer3               | Timer3               | Timer3               |

| 00 0223 0080 | 00 0223 FFFF  | 64K-128  | Reserved             | Reserved             | Reserved             |

| 00 0224 0000 | 00 0224 007F  | 128      | Reserved             | Reserved             | Reserved             |

| 00 0224 0080 | 00 0224 FFFF  | 64K-128  | Reserved             | Reserved             | Reserved             |

| 00 0225 0000 | 00 0225 007F  | 128      | Reserved             | Reserved             | Reserved             |

| 00 0225 0080 | 00 0225 FFFF  | 64K-128  | Reserved             | Reserved             | Reserved             |

| 00 0226 0000 | 00 0226 007F  | 128      | Reserved             | Reserved             | Reserved             |

| 00 0226 0080 | 00 0226 FFFF  | 64K-128  | Reserved             | Reserved             | Reserved             |

| 00 0227 0000 | 00 0227 007F  | 128      | Reserved             | Reserved             | Reserved             |

| 00 0227 0080 | 00 0227 FFFF  | 64K-128  | Reserved             | Reserved             | Reserved             |

| 00 0228 0000 | 00 0228 007F  | 128      | Timer 8              | Timer 8              | Timer 8              |

| 00 0228 0080 | 00 0228 FFFF  | 64K-128  | Reserved             | Reserved             | Reserved             |

| 00 0229 0000 | 00 0229 007F  | 128      | Timer 9              | Timer 9              | Timer 9              |

| 00 0229 0080 | 00 0229 FFFF  | 64K-128  | Reserved             | Reserved             | Reserved             |

| 00 022A 0000 | 00 022A 007F  | 128      | Timer 10             | Timer 10             | Timer 10             |

| 00 022A 0080 | 00 022A FFFF  | 64K-128  | Reserved             | Reserved             | Reserved             |

| 00 022B 0000 | 00 022B 007F  | 128      | Timer 11             | Timer 11             | Timer 11             |

| 00 022B 0080 | 00 022B FFFF  | 64K-128  | Reserved             | Reserved             | Reserved             |

| 00 022C 0000 | 00 022C 007F  | 128      | Timer 12             | Timer 12             | Timer 12             |

| 00 022C 0080 | 00 022C FFFF  | 64K-128  | Reserved             | Reserved             | Reserved             |

| 00 022D 0000 | 00 022D 007F  | 128      | Timer 13             | Timer 13             | Timer 13             |

| 00 022D 0080 | 00 022D FFFF  | 64K-128  | Reserved             | Reserved             | Reserved             |

| 00 022E 0000 | 00 022E 007F  | 128      | Timer 14             | Timer 14             | Timer 14             |

| 00 022E 0080 | 00 022E FFFF  | 64K-128  | Reserved             | Reserved             | Reserved             |

| 00 022F 0000 | 00 022F 007F  | 128      | Timer 15             | Timer 15             | Timer 15             |

| 00 022F 0080 | 00 022F 00FF  | 128      | Timer 16             | Timer 16             | Timer 16             |

| 00 022F 0100 | 00 022F 017F  | 128      | Timer 17             | Timer 17             | Timer 17             |

| 00 022F 0180 | 00 022F 01FF  | 128      | Reserved             | Reserved             | Reserved             |

| 00 022F 0200 | 00 022F 027F  | 128      | Reserved             | Reserved             | Reserved             |

| 00 0230 0000 | 00 0230 FFFF  | 64K      | Reserved             | Reserved             | Reserved             |

| Physical 40  | bit Address  |         |                                    |                                    |                                    |

|--------------|--------------|---------|------------------------------------|------------------------------------|------------------------------------|

| Start        | End          | Bytes   | ARM View                           | DSP View                           | SOC View                           |

| 00 0231 0000 | 00 0231 01FF | 512     | PLL Controller                     | PLL Controller                     | PLL Controller                     |

| 00 0231 0200 | 00 0231 9FFF | 40K-512 | Reserved                           | Reserved                           | Reserved                           |

| 00 0231 A000 | 00 0231 BFFF | 8K      | Reserved                           | Reserved                           | Reserved                           |

| 00 0231 C000 | 00 0231 DFFF | 8K      | Reserved                           | Reserved                           | Reserved                           |

| 00 0231 E000 | 00 0231 FFFF | 8K      | Reserved                           | Reserved                           | Reserved                           |

| 00 0232 0000 | 00 0232 1FFF | 8K      | CSISC2 SerDes Config 3             | CSISC2 SerDes Config 3             | CSISC2 SerDes Config 3             |

| 00 0232 2000 | 00 0232 3FFF | 8K      | Reserved                           | Reserved                           | Reserved                           |

| 00 0232 4000 | 00 0232 5FFF | 8K      | CSISC2 SerDes Config 0             | CSISC2 SerDes Config 0             | CSISC2 SerDes Config 0             |

| 00 02326000  | 00 0232 7FFF | 4K      | CSISC2 SerDes Config 1             | CSISC2 SerDes Config 1             | CSISC2 SerDes Config 1             |

| 00 0232 8000 | 00 0232 8FFF | 8K      | Reserved                           | Reserved                           | Reserved                           |

| 00 0232 9000 | 00 0232 9FFF | 4K      | DDRA PHY Config                    | DDRA PHY Config                    | DDRA PHY Config                    |

| 00 0232 A000 | 00 0232 BFFF | 8K      | CSISC2 SerDes Config 2             | CSISC2 SerDes Config 2             | CSISC2 SerDes Config 2             |

| 00 0232 C000 | 00 0232 CFFF | 4K      | Reserved                           | Reserved                           | Reserved                           |

| 00 0232 D000 | 00 0232 DFFF | 4K      | Reserved                           | Reserved                           | Reserved                           |

| 00 0232 E000 | 00 0232 EFFF | 4K      | Reserved                           | Reserved                           | Reserved                           |

| 00 0232 F000 | 00 0232 FFFF | 4K      | Reserved                           | Reserved                           | Reserved                           |

| 00 0233 0000 | 00 0233 03FF | 1K      | SmartReflex0                       | SmartReflex0                       | SmartReflex0                       |

| 00 0233 0400 | 00 0233 07FF | 1K      | Reserved                           | Reserved                           | Reserved                           |

| 00 0233 0400 | 00 0233 FFFF | 62K     | Reserved                           | Reserved                           | Reserved                           |

| 00 0234 0000 | 00 0234 03FF | 1K      | Memory protection unit (MPU)<br>15 | Memory protection unit (MPU)<br>15 | Memory protection unit<br>(MPU) 15 |

| 00 0234 0400 | 00 0234 07FF | 1K      | Reserved                           | Reserved                           | Reserved                           |

| 00 0234 0800 | 00 0234 087F | 128     | Tracer CFG30                       | Tracer CFG30                       | Tracer CFG30                       |

| 00 0234 0880 | 00 0234 0BFF | 1K-128  | Reserved                           | Reserved                           | Reserved                           |

| 00 0234 0C00 | 00 0234 3FFF | 13K     | Reserved                           | Reserved                           | Reserved                           |

| 00 0234 4000 | 00 0234 7FFF | 16K     | Reserved                           | Reserved                           | Reserved                           |

| 00 0234 8000 | 00 0234 80FF | 256     | GPIO1 configuration                | GPIO1 configuration                | GPIO1 configuration                |

| 00 0234 8100 | 00 0234 83FF | 768     | Reserved                           | Reserved                           | Reserved                           |

| 00 0234 8400 | 00 0234 843F | 64      | UART2 configuration                | UART2 configuration                | UART2 configuration                |

| 00 02348440  | 00 0234 87FF | 1K-64   | Reserved                           | Reserved                           | Reserved                           |

| 00 0234 8800 | 00 0234 883F | 64      | UART3 configuration                | UART3 configuration                | UART3 configuration                |

| 00 0234 8840 | 00 0234 8BFF | 1K-64   | Reserved                           | Reserved                           | Reserved                           |

| 00 0234 8C00 | 00 0234 8FFF | 1K      | OSR configuration                  | OSR configuration                  | OSR configuration                  |

| 00 0234 9000 | 00 0234 FFFF | 28K     | Reserved                           | Reserved                           | Reserved                           |

| 00 0235 0000 | 00 0235 0FFF | 4K      | Power sleep controller (PSC)       | Power sleep controller (PSC)       | Power sleep controller (PSC)       |

| 00 0235 1000 | 00 0235 FFFF | 64K-4K  | Reserved                           | Reserved                           | Reserved                           |

| 00 0236 0000 | 00 0236 03FF | 1K      | Memory protection unit (MPU) 0     | Memory protection unit (MPU) 0     | Memory protection unit<br>(MPU) 0  |

| 00 0236 0400 | 00 0236 7FFF | 31K     | Reserved                           | Reserved                           | Reserved                           |

| 00 0236 8000 | 00 0236 83FF | 1K      | Memory protection unit (MPU) 1     | Memory protection unit (MPU) 1     | Memory protection unit<br>(MPU) 1  |

| 00 0236 8400 | 00 0236 FFFF | 31K     | Reserved                           | Reserved                           | Reserved                           |

| 00 0237 0000 | 00 0237 03FF | 1K      | Memory protection unit (MPU) 2     | Memory protection unit (MPU) 2     | Memory protection unit (MPU) 2     |

| Physical 40                  | ) bit Address |        |                                    |                                    |                                    |

|------------------------------|---------------|--------|------------------------------------|------------------------------------|------------------------------------|

| Start                        | End           | Bytes  | ARM View                           | DSP View                           | SOC View                           |

| 00 0237 0400                 | 00 0237 7FFF  | 31K    | Reserved                           | Reserved                           | Reserved                           |

| 00 0237 8000                 | 00 0237 83FF  | 1K     | Memory protection unit (MPU) 3     | Memory protection unit (MPU) 3     | Memory protection unit<br>(MPU) 3  |

| 00 0237 8400                 | 00 0237 FFFF  | 31K    | Reserved                           | Reserved                           | Reserved                           |

| 00 0238 0000                 | 00 0238 03FF  | 1K     | Memory protection unit (MPU) 4     | Memory protection unit (MPU) 4     | Memory protection unit<br>(MPU) 4  |

| 00 0238 8000                 | 00 0238 83FF  | 1K     | Memory protection unit (MPU) 5     | Memory protection unit (MPU) 5     | Memory protection unit<br>(MPU) 5  |

| 00 0238 8400                 | 00 0238 87FF  | 1K     | Memory protection unit (MPU) 6     | Memory protection unit (MPU) 6     | Memory protection unit<br>(MPU) 6  |

| 00 0238 8800                 | 00 0238 8BFF  | 1K     | Memory protection unit (MPU) 7     | Memory protection unit (MPU) 7     | Memory protection unit<br>(MPU) 7  |

| 00 0238 8C00                 | 00 0238 8FFF  | 1K     | Memory protection unit (MPU) 8     | Memory protection unit (MPU) 8     | Memory protection unit<br>(MPU) 8  |

| 00 0238 9000                 | 00 0238 93FF  | 1K     | Memory protection unit (MPU) 9     | Memory protection unit (MPU) 9     | Memory protection unit<br>(MPU) 9  |

| 00 0238 9400                 | 00 0238 97FF  | 1K     | Memory protection unit (MPU)<br>10 | Memory protection unit (MPU)<br>10 | Memory protection unit<br>(MPU) 10 |

| 00 0238 9800                 | 00 0238 9BFF  | 1K     | Memory protection unit (MPU)<br>11 | Memory protection unit (MPU)<br>11 | Memory protection unit<br>(MPU) 11 |

| 00 0238 9C00                 | 00 0238 9FFF  | 1K     | Memory protection unit (MPU)<br>12 | Memory protection unit (MPU)<br>12 | Memory protection unit<br>(MPU) 12 |

| 00 0238 A000                 | 00 0238 A3FF  | 1K     | Memory protection unit (MPU)<br>13 | Memory protection unit (MPU)<br>13 | Memory protection unit<br>(MPU) 13 |

| 00 0238 A400                 | 00 0238 A7FF  | 1K     | Memory protection unit (MPU)<br>14 | Memory protection unit (MPU)<br>14 | Memory protection unit<br>(MPU) 14 |

| 00 0238 A800                 | 00 023F FFFF  | 471K   | Reserved                           | Reserved                           | Reserved                           |

| 00 0240 0000                 | 00 0243 FFFF  | 256K   | Reserved                           | Reserved                           | Reserved                           |

| 00 0244 0000                 | 00 0244 3FFF  | 16K    | DSP trace formatter 0              | DSP trace formatter 0              | DSP trace formatter 0              |

| 00 0244 4000                 | 00 0244 FFFF  | 48K    | Reserved                           | Reserved                           | Reserved                           |

| 00 0245 0000                 | 00 0245 3FFF  | 16K    | DSP trace formatter 1              | DSP trace formatter 1              | DSP trace formatter 1              |

| 00 0245 4000                 | 00 0245 FFFF  | 48K    | Reserved                           | Reserved                           | Reserved                           |

| 00 0246 0000                 | 00 0246 3FFF  | 16K    | DSP trace formatter 2              | DSP trace formatter 2              | DSP trace formatter 2              |

| 00 0246 4000                 | 00 0246 FFFF  | 48K    | Reserved                           | Reserved                           | Reserved                           |

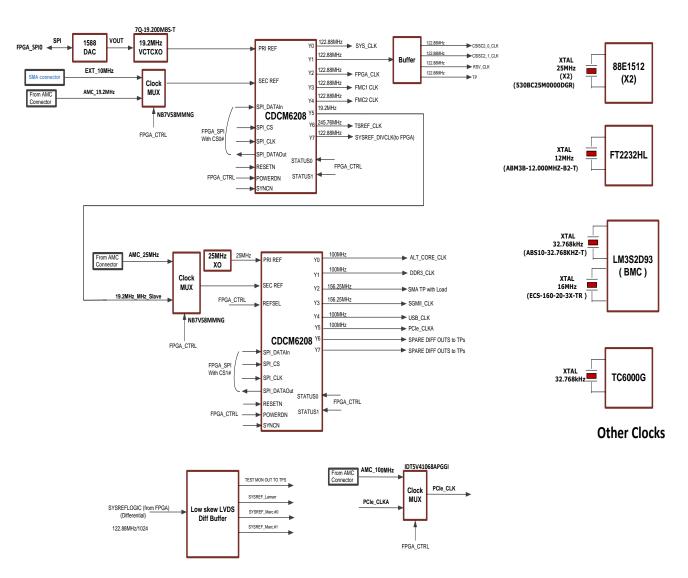

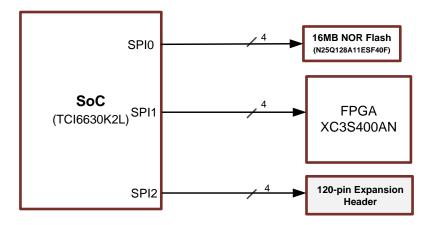

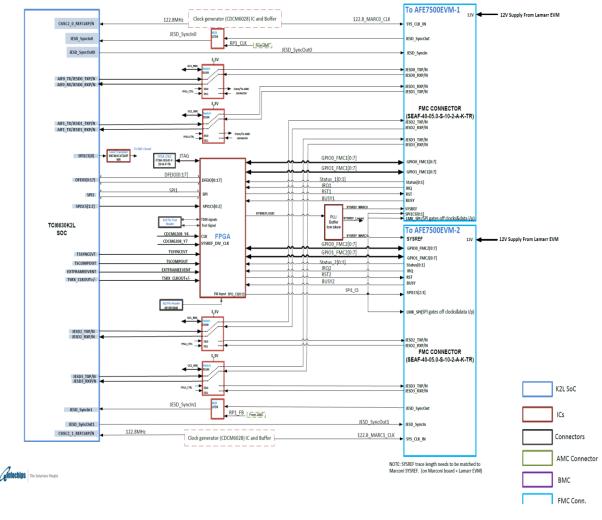

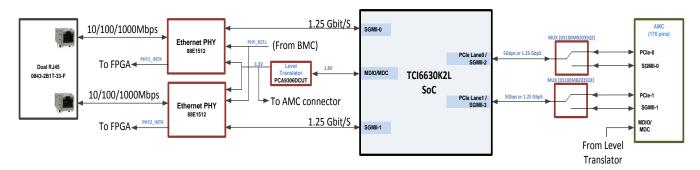

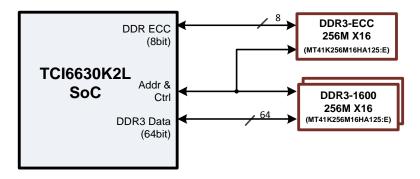

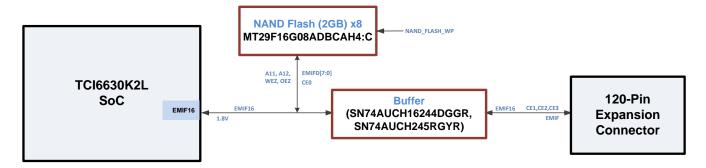

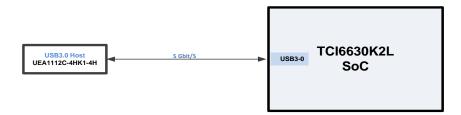

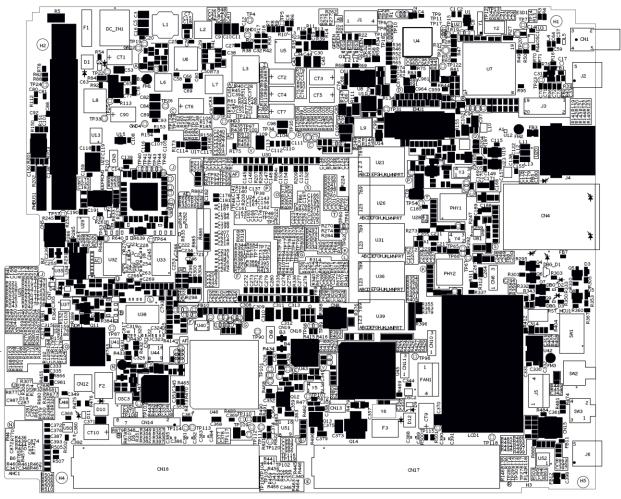

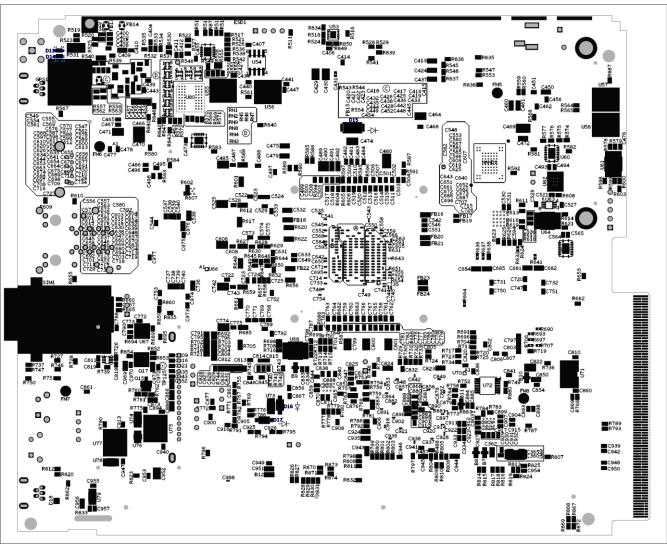

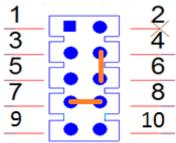

| 00 0247 0000                 | 00 0247 3FFF  | 16K    | DSP trace formatter 3              | DSP trace formatter 3              | DSP trace formatter 3              |