Executive Summary

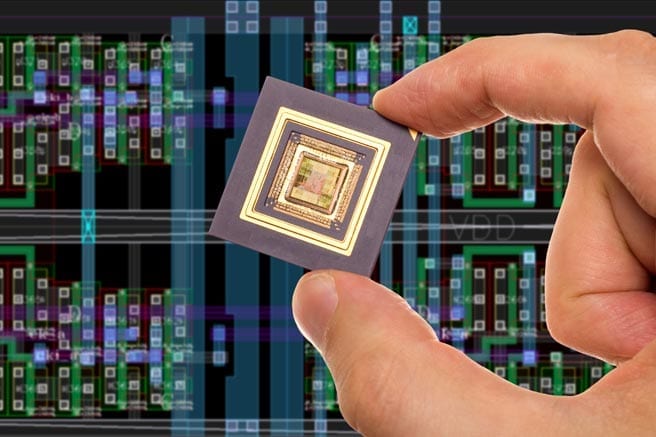

The client is a global supplier of Automated Testing Equipment (ATE) for some of the world’s most prestigious semiconductor companies. To meet its goal of developing faster, next-gen ATE instruments, it was working on a series of internal IPs, out of which a mixed signal ASIC chip with 40 nm pattern/timing generator and industry-wide high speed interfaces, emerged as a turnkey innovation. At once, time-to-market assumed key significance, and the client started looking for a partner to speedily ramp up its existing verification environment.

eInfochips enabled a highly configurable, scalable and intelligent verification environment in ASIC for the client, leading to enhanced verification coverage in a much shorter time. This also fulfilled Automatic Test Pattern Generation (ATPG) effectiveness criteria because thorough verification was achieved at block level (more than 20 internal blocks), cluster level, SoC-digital level, SoC-Chip level (Digital + Analog) and System Sim level. A critical architectural bug was found in the designs related to bandwidth verification.

Project Highlights

- Targeted for Leading Automated Test Equipment (ATE) Client

- 40nm Pattern/Timing Generator Mixed ASIC

- 2.4 Gbps Max Throughput; 400 Mhz Operating frequency

- 2.2 GHz Data Bandwidth

- Over 100 million gates in Digital Mode